US009531282B1

# (12) United States Patent

**Nikitin**

(10) Patent No.: US 9,531,282 B1

(45) **Date of Patent:**

Dec. 27, 2016

## (54) METHOD AND APPARATUS FOR REGULATED THREE-PHASE AC-TO-DC CONVERSION WITH HIGH POWER FACTOR AND LOW HARMONIC DISTORTIONS

(71) Applicant: Avatekh, Inc., Lawrence, KS (US)

(72) Inventor: Alexei V. Nikitin, Lawrence, KS (US)

(73) Assignee: Avatekh, Inc., Lawrence, KS (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/086,411

(22) Filed: Mar. 31, 2016

### Related U.S. Application Data

- (60) Provisional application No. 62/142,910, filed on Apr. 3, 2015.

- (51) Int. Cl.

H02M 3/335 (2006.01)

H02M 7/04 (2006.01)

H02M 1/42 (2007.01)

H02M 1/44 (2007.01)

H02M 1/12 (2006.01)

(52) **U.S. Cl.**

(58) Field of Classification Search

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| A *  | 6/1998             | Barrett H02M 1/4241               |

|------|--------------------|-----------------------------------|

|      |                    | 363/132                           |

| A *  | 12/1998            | Swamy H02J 3/01                   |

| 4.1  | 12/1/20            | 333/175                           |

|      |                    |                                   |

| A *  | 6/1999             | Jiang H02M 1/4208                 |

|      |                    | 323/267                           |

| A *  | 7/1000             | Guerrera G05F 1/70                |

| A    | //1999             |                                   |

|      |                    | 323/222                           |

| B2 * | 1/2012             | Moon H02M 1/4225                  |

| 1)2  | 1/2012             |                                   |

|      |                    | 363/70                            |

| A1   | 5/2012             | Cuk                               |

| A 1  | 7/2014             | Flam                              |

|      |                    |                                   |

| ΑI   | 1/2015             | Ganev et al.                      |

|      | A * A * B2 * A1 A1 | A * 12/1998 A * 6/1999 A * 7/1999 |

#### OTHER PUBLICATIONS

Kolar, J.W.; Muhlethaler, J.; "The Essence of Three-Phase PFC Rectifier Systems", Swiss Fed Institute of Tech Zurich, Power Elec Systems Lab, www.pes.ee.ethz.ch, 2012.

S. Ramamoorthy, "Improved Three Phase AC-DC Converter w/Power Factor & Harmonics Correction"; Middle-East Journal of Scientific Research—2014, pp. 1597-1604, Dept of EEE, Bharath Univ., Chennai-73, India, ISSN 1990-9233.

## \* cited by examiner

Primary Examiner — Jue Zhang (74) Attorney, Agent, or Firm — Erickson Kernell IP, LLC

## (57) ABSTRACT

The present invention relates to methods and corresponding apparatus for efficient 3-phase AC to DC conversion with high power quality, for example, high power factor and low harmonic distortions. The invention further relates to methods and corresponding apparatus for regulation and control of said AC to DC conversion.

## 24 Claims, 44 Drawing Sheets

Fig. 1

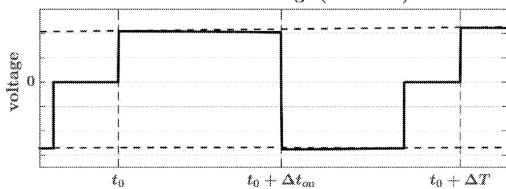

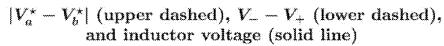

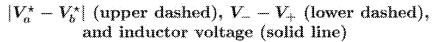

$|V_a - V_b|$  (upper dashed),  $V_- - V_+$  (lower dashed), and inductor voltage (solid line)

Fig. 2

Fig. 3

Fig. 4

# $L_{ m max}$ vs. voltage conversion ratio

Fig. 5

Fig. 6

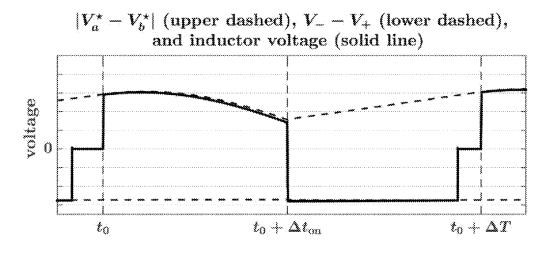

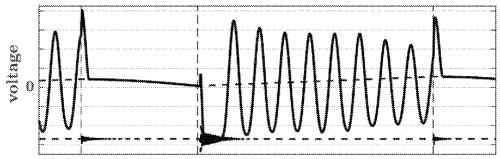

$|V_a^{\star}-V_b^{\star}|$  (upper dashed),  $V_--V_+$  (lower dashed), and inductor voltage (solid line)

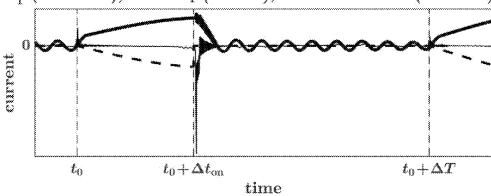

Fig. 7

Fig. 8

Fig. 9

Fig. 15

Fig. 16

Fig. 17

Fig. 18

Dec. 27, 2016

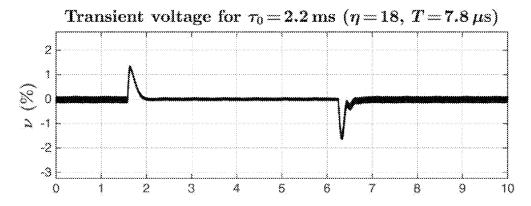

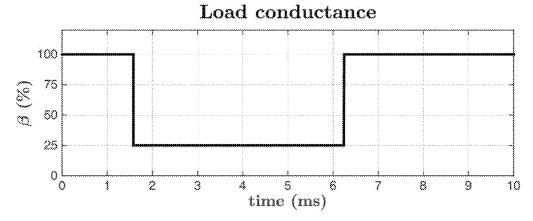

Fig. 22

Fig. 23

Fig. 24

Fig. 25

-3 0

10

2

3

4

5

6

8

Fig. 26

Fig. 27

Fig. 28

Fig. 29

Fig. 30

Fig. 31

Fig. 32

Fig. 35

Fig. 36

Fig. 37

$I_1^*$  (thick line), 'ideal'  $I_1$  (dashed), and CM current (thin line)

. w /.

Fig. 38

Fig. 39

Fig. 40

Fig. 41

Fig. 42

Fig. 43

Fig. 44

# METHOD AND APPARATUS FOR REGULATED THREE-PHASE AC-TO-DC CONVERSION WITH HIGH POWER FACTOR AND LOW HARMONIC DISTORTIONS

# CROSS REFERENCES TO RELATED APPLICATIONS

This application claims the benefit of the U.S. provisional patent application 62/142,910 filled on 3 Apr. 2015, which is incorporated herein by reference in its entirety.

## STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

None.

## COPYRIGHT NOTIFICATION

Portions of this patent application contain materials that are subject to copyright protection. The copyright owner has no objection to the facsimile reproduction by anyone of the patent document or the patent disclosure, as it appears in the Patent and Trademark Office patent file or records, but <sup>25</sup> otherwise reserves all copyright rights whatsoever.

## TECHNICAL FIELD

The present invention relates to methods and corresponding apparatus for efficient 3-phase AC to DC conversion with high power quality, for example, high power factor and low harmonic distortions. The invention further relates to methods and corresponding apparatus for regulation and control of said AC to DC conversion.

#### BACKGROUND

AC/DC converters may be widely used in many types of industry. For example, in many applications electrical power 40 for components in a system may be provided using AC generators. Because certain types of components (or loads) may not use AC power, it would be common to rectify AC power to obtain DC power. Rectification, however, may not be accomplished with 100% efficiency, and typically results 45 in reduction in power quality, for example, reduction in power factor and in increased harmonic distortions of the line currents. In many applications, the power quality may need to be at or above a certain level in order to prevent disturbance to other loads on the system.

For example, there is an increasing need for high power 3-phase AC/DC converters for the next generation of More Electric Aircraft (MEA). New standards for the power factor and, more importantly, the limits on the reflected current harmonics imposed by DO-160, Environmental Conditions 55 and Test Procedures for Airborne Equipment, call for development of AC/DC converters, including those based on active power factor correction (PFC) topologies, that satisfy these stringent requirements.

Further, certain applications may have constraints on 60 and/or requirements regarding the output power, weight, size, cost, complexity, and reliability, and on the electromagnetic compatibility (EMC) and electromagnetic interference (EMI) emissions of AC/DC converters.

There typically exist various other, often conflicting 65 requirements on AC/DC conversion. Those may include, but are not limited to, requirements on different voltage conver-

2

sion ratios (e.g., from 115 VAC to 270 VDC, or from 230 VAC to 540 VDC), "wild" frequency compatibility (i.e., the ability to convert AC power that varies in time in a wide frequency range, e.g., from 300 Hz to 800 Hz), output voltage ripple, soft start ability (e.g., for powering motors), over-current protection, cooling method(s), and environmental requirements/qualifications.

Power conversion technologies that are capable of meeting enhanced power quality requirements may be characterized as passive conversion, active conversion, and "hybrid" conversion employing harmonic correction techniques such as those based on harmonic injection and/or active filter implementation. An overview of different approaches to constructing three-phase rectifier systems may be found in, e.g., [3] and the references thereof.

For example, passive AC/DC power conversion may be accomplished with a plurality of diode pairs, where each pair is connected to a different phase of the AC input, to provide a rectified DC output. However, this type of AC/DC conversion may lead to substantial current harmonics that would pollute the electric power generation and distribution system. One solution to the foregoing problem may be to increase the number of supply phases for rectification.

To reduce current harmonics, multi-phase transformers (Transformer Rectifier Units, or TRUs) and/or autotransformers (Auto-Transformer Rectifier Units, or ATRUs) may be employed to increase the number of AC phases supplied to the rectifier unit. For example, in an 18-pulse passive AC/DC converter (18-pulse TRU/ATRU) the transformer/autotransformer may be used to transform the three-phase AC input whose phases are spaced at 1200, into a system with nine phases spaced at 40°. This would have the effect of reducing the harmonics associated with the AC/DC sonversion.

Passive multi-phase harmonic reduction typically has the advantages of relative simplicity and low cost, absence of or reduced need for energy storage devices and/or control, high reliability (e.g., typical mean time between failures (MTBF) in excess of 100,000 hours), robustness (e.g., the ability to accepts high overloads), and low weight at high line frequencies (e.g., at 400 Hz and higher).

An absence of output voltage regulation may be viewed as the main disadvantage of passive conversion. Without such regulation, input voltage variations are proportionally passed to the output, and a change in the load would also result in a change in the output voltage. For example, in a passive converter from 115 VAC to 270 VDC a typical difference in the output voltage between no load to full load conditions may be approximately 4% to 6%, or 11 VDC to 16 VDC. To obtain output voltage regulation, an additional active DC/DC converter stage would need to follow a passive AC/DC converter stage, which would increase complexity, weight, and cost, and would decrease efficiency, robustness, and reliability of the converter. Also, the absence of regulation may result in presence of significant inrush currents.

To overcome certain limitations of passive conversion, various active conversion means may be employed, in addition or as an alternative to passive conversion. Such means may include, for example, harmonic correction techniques based on harmonic injection and/or active filter implementation.

As a main alternative to passive AC/DC converters, active (e.g., high frequency switch mode) AC/DC conversion may also be used, and such active conversion would be capable of providing regulated DC output voltage.

Output voltage regulation and/or adjustment may be considered the main advantage of active conversion. Also, active regulation topologies may operate in a wide range of line frequencies (e.g., the same active AC/DC converter may be used for 300 Hz, 800 Hz, and/or 50/60 Hz), and would 5 typically have a built-in soft start ability, over-current protection, current limiting, and thermal protection. In addition, active AC/DC converters may have significantly lower weight for low AC frequency conversion in comparison with passive converters designed for such low frequencies.

The disadvantages of active converters may include higher cost and lower reliability, the need for high energy storage capacitor(s), and lower overload capabilities in comparison with passive conversion. In addition, active AC/DC converters may not easily accomplish conversion at some 15 voltage conversion ratios.

For example, two typical active approaches may include boost (step-up) and buck (step-down) conversion. For a 115 VAC line-to-neutral 3-phase input voltage, a boost converter would be capable of providing ≥320 VDC output, while a 20 buck converter would be capable of providing ≤230 VDC output. Thus the output voltage range from 230 VDC to 320 VDC may not be available without an additional DC/DC conversion stage.

Depending on the converter topology, the output power 25 requirements, and the AC/DC voltage conversion ratios, practical state-of-art passive, hybrid, and active AC/DC converters would provide the input-current total harmonic distortion (THD) in a typical range of 3% to 12%. Further reduction of the THD (to, e.g., 1% to 2% range) may require 30 more complicated multi-stage and/or multi-level approaches, with typically more than three active power switches, increased complexity and cost, and decreased robustness and reliability.

In addition, state-of-art active AC/DC converters targeting high power quality may require complicated regulation and control topologies, e.g., those utilizing variable switching frequency, fuzzy logic, and/or multiple feedback control loops.

## **SUMMARY**

The present invention disclosed herein may be referred to as an Ultra Linear Switching Rectifier, or ULSR, where "ultra" may refer to very or extremely, "linear" may refer to 45 proportional relation between input currents and voltages, and thus imply high power factor (PF) and low total harmonic distortion (THD), "switching" may refer to active (solid state) switching, and "rectifier" may refer to AC/DC conversion.

The ULSR may be viewed as a unidirectional three-phase three-switch pulse-width modulation (PWM) rectifier with controlled output voltage. It may also be viewed as a three-phase diode bridge with an integrated buck-boost converter.

The ULSR offers a wide range of technical and commercial advantages over the state-of-art solutions that may include, but are not limited to, the following:

(i) Efficient 3-phase AC-to-DC conversion with high power factor (e.g.,  $\geq$ 99.9%) and low harmonic distortions 60 (e.g.,  $\leq$ 0.5%) for a wide range of line frequencies (e.g., from 50 Hz to 1 kHz), output powers (e.g., from zero to  $\geq$ 10 kW), and voltage conversion ratios; (ii) various standard and custom conversion voltages, including step-up and step-down conversion, and the output voltages corresponding to 65 those of a three-phase full-wave diode rectifier ( $V_{out}/V_{LN}\approx$ 2.34, e.g., 115 VAC to 270 VDC, or 230 VAC to 540

4

VDC); (iii) both non-isolated and isolated topologies with similar complexity, power densities, and other properties; (iv) low complexity, low realization effort; (v) lightweight and rugged "all-solid-state" design; (vi) three-wire input, no connection to neutral; (vii) low EMI emissions; (viii) "wild" line frequency compatibility; (ix) well distributed and equalized currents through active and passive components; (x) flexible cooling options (e.g., forced air, fan, cold plate, liquid cooling); (xi) flexible options for component technologies (e.g., conventional Si devices, SiC- or GaN-based semiconductors, diodes or actively controlled switches, air or magnetic core inductors); (xii) large acceptable tolerances and long-term drifts; (xiii) reliable behavior under heavily unbalanced mains voltages and in case of mains failure; (xiv) ability to easily connect various ULSR converters (of the same and/or different power ratings) in parallel to increase power and/or to provide N+1 redundancy.

While a variety of state-of-art fixed and/or variable switching frequency (e.g., in a 40 kHz to 500 kHz range) PWM controllers may be used with ULSRs to provide a regulated output voltage, the present invention also discloses a simple, robust, and stable analog fixed-frequency PWM controller, with a common control signal to all three switches, that is tailored to the ULSR topology. Said controller requires only output voltage feedback control loop (but may also include an additional load current feedback to improve transient response of the ULSR to the changes in the load), and is capable of providing a regulated ULSR output voltage for full range of output power (i.e. from full load to open circuit), with small amplitude and short duration voltage and current transients in response to load changes.

Further scope and the applicability of the invention will be clarified through the detailed description given hereinafter. It should be understood, however, that the specific examples, while indicating preferred embodiments of the invention, are presented for illustration only. Various changes and modifications within the spirit and scope of the invention should become apparent to those skilled in the art from this detailed description. Furthermore, all the mathematical expressions, and the examples of hardware implementations are used only as a descriptive language to convey the inventive ideas clearly, and are not limitative of the claimed invention.

## BRIEF DESCRIPTION OF FIGURES

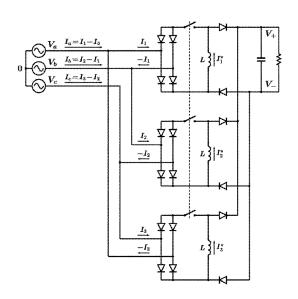

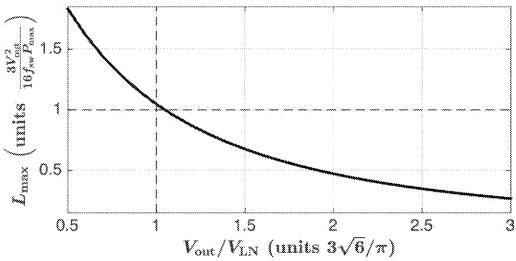

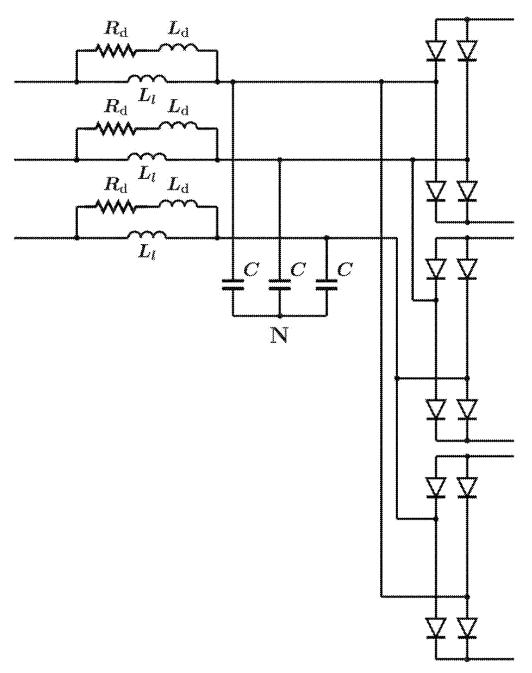

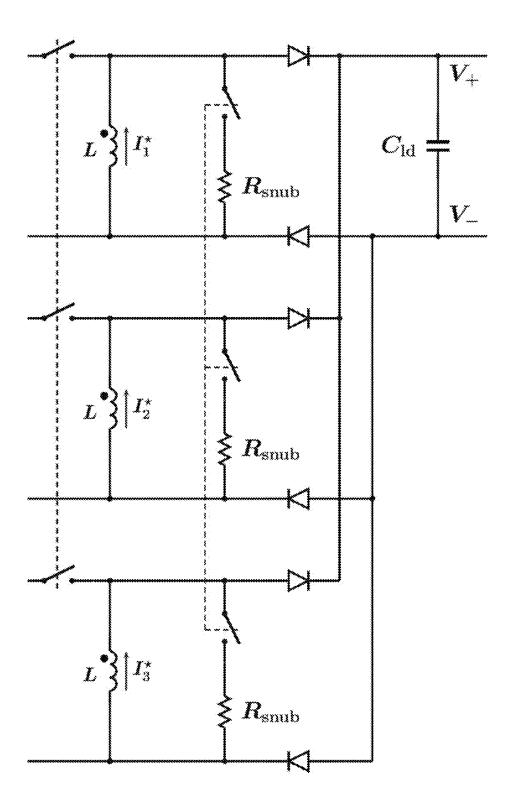

FIG. 1. Initial idealized circuit diagram of a 3-phase AC/DC converter of the current invention.

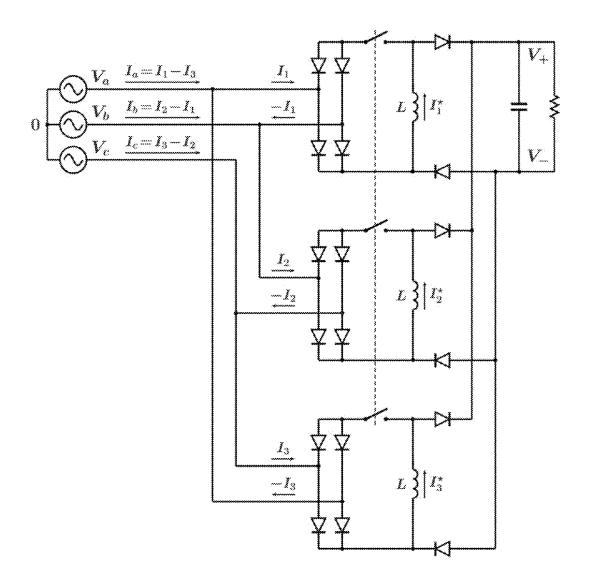

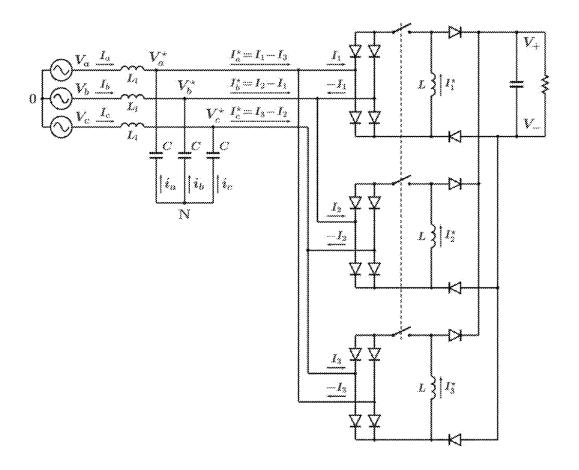

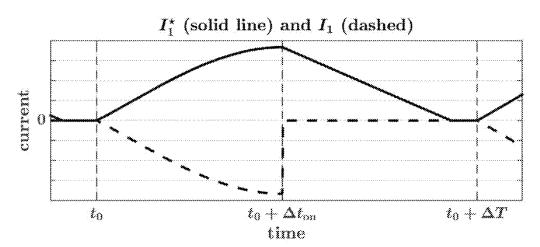

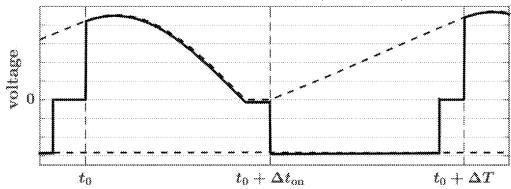

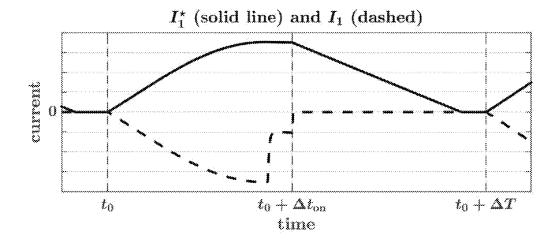

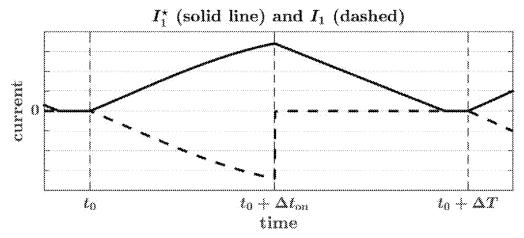

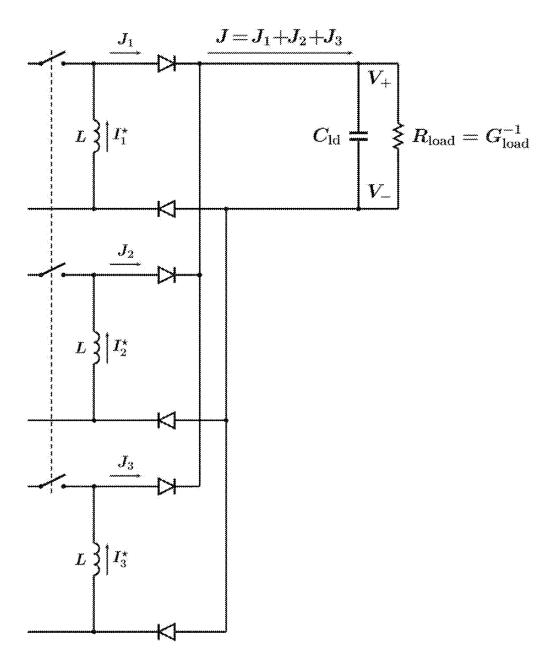

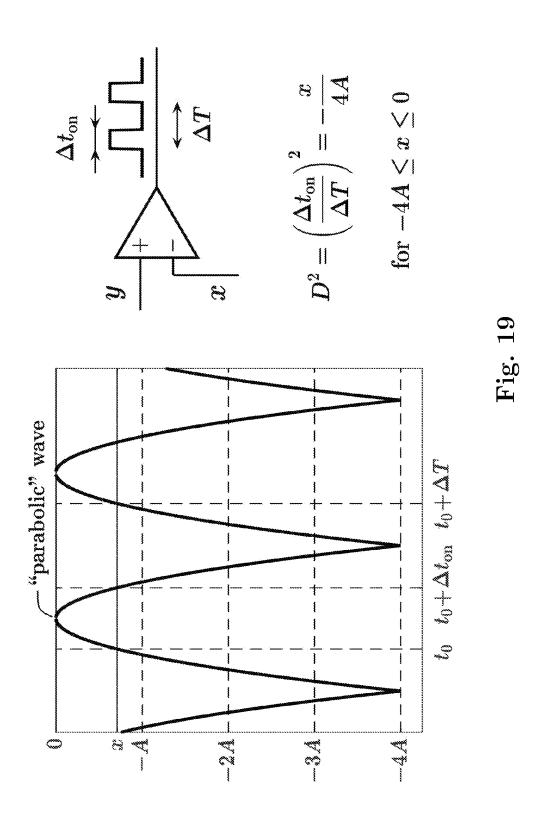

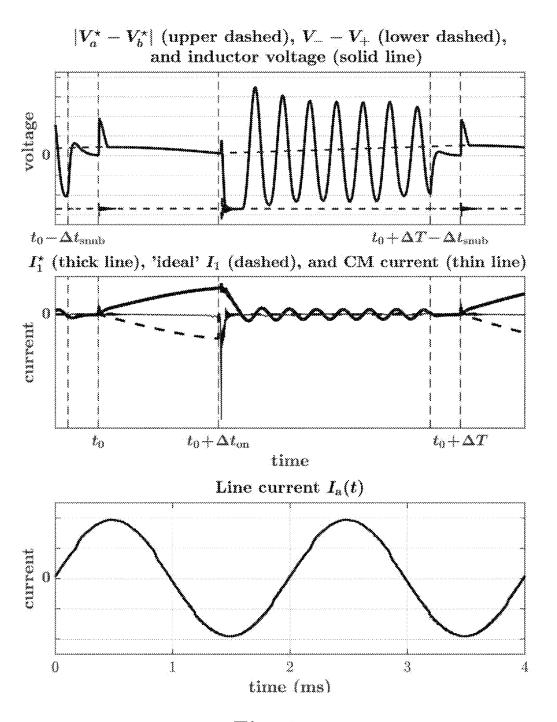

FIG. 2. Voltage and current relations during switching for the inductor in the 1st section.

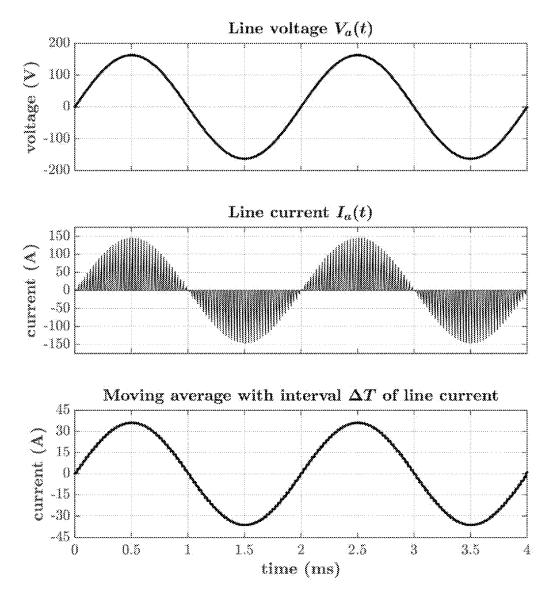

FIG. 3. Line voltage (upper panel), line current (middle panel), and moving average of line current (lower panel) for the converter shown in FIG. 1.

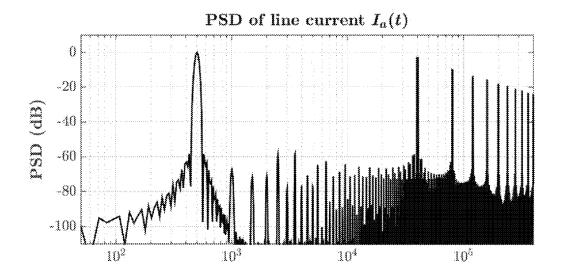

FIG. **4.** PSDs of line current (upper panel) and of moving average of line current (lower panel) for the converter shown in FIG. **1**

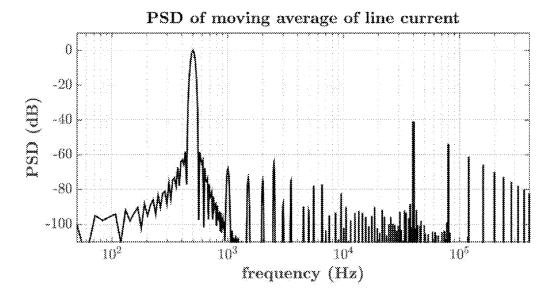

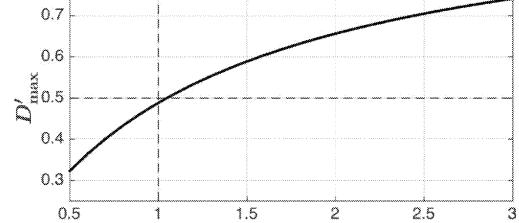

FIG. 5. Maximum duty cycle  $D_{max}^{t}$  (upper panel) and maximum value of the converter inductance  $L_{max}$  (lower panel) according to equations (12) and (14), respectively, as functions of the voltage conversion ratio  $V_{out}/V_{LN}$ .

FIG. 6. 3-phase AC-to-DC converter shown in FIG. 1 with an LC filtering network inserted between the voltage sources and the power stage of the converter.

FIG. 7. Example of voltage and current relations during switching for the inductor in the 1st section of the converter shown in FIG. 6 with  $C = C_{min}(V_{LN})$ .

- FIG. 8. Example of voltage and current relations during switching for the inductor in the 1st section of the converter shown in FIG. 6 with  $C \approx \frac{3}{4} C_{min}$  ( $V_{LN} = min(V_{LN})$ ).

- FIG. 9. Example of voltage and current relations during switching for the inductor in the 1st section of the converter 5 shown in FIG. 6 with  $C \approx 2C_{min} (V_{LN} = min(V_{LN}))$ .

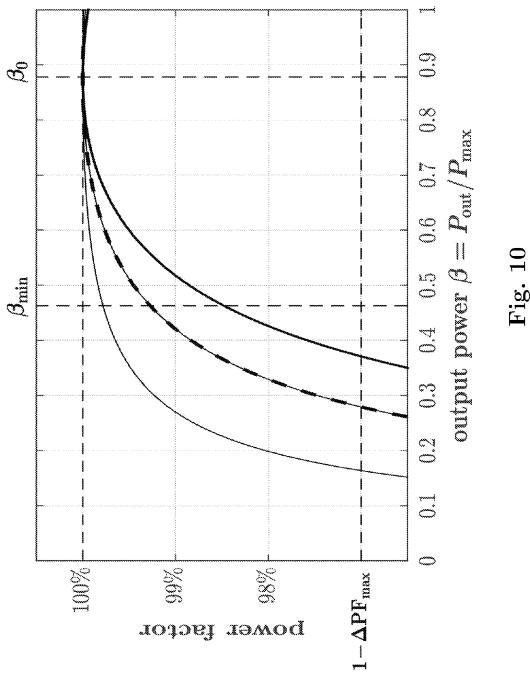

- FIG. 10. Power factors as functions of output power for  $\gamma$ =2, max(f<sub>4C</sub>)=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{sw}$ =48 kHz. The line inductance is according to 10 equation (44).

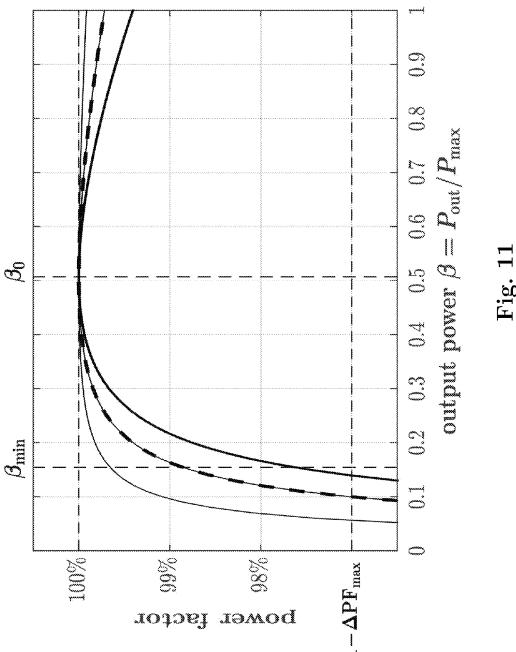

- FIG. 11. Power factors as functions of output power for  $\gamma$ =2, max(f<sub>AC</sub>)=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching equation (44).

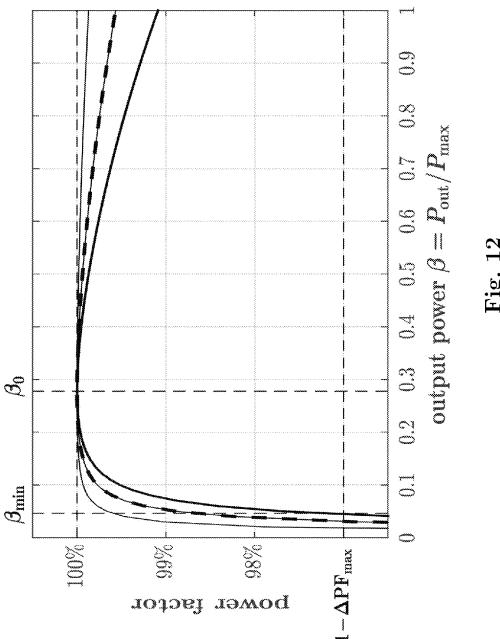

- FIG. 12. Power factors as functions of output power for  $\gamma$ =2, max(f<sub>AC</sub>)=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{sw}$ =480 kHz. The line inductance is according to 20 the 1st section converter inductor voltage and current, and equation (44).

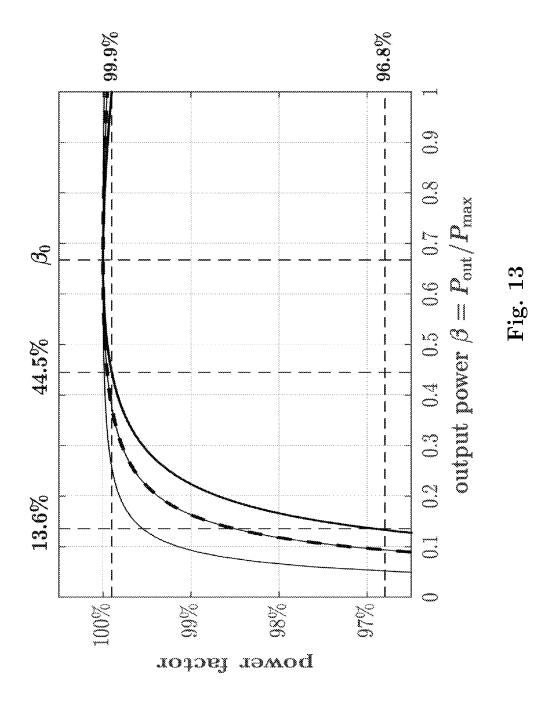

- FIG. 13. Power factors as functions of output power for  $\gamma=1.9$ , max( $f_{AC}$ )=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{sw}$ =144 kHz. The line inductance is according 25 to equation (41).

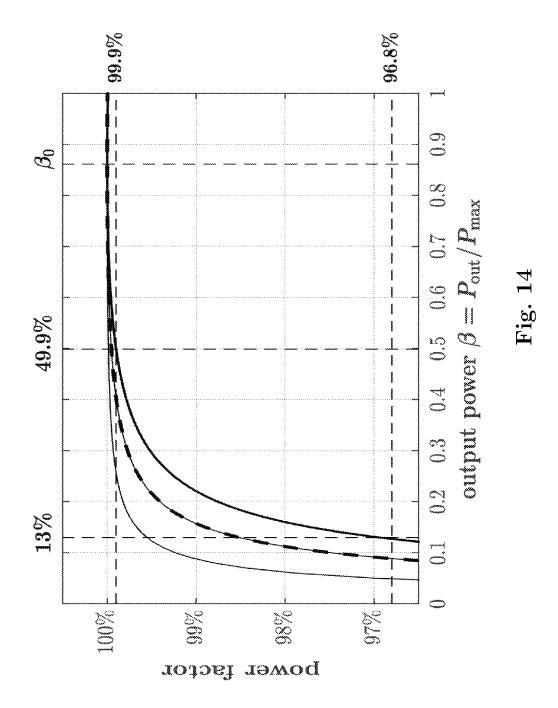

- FIG. 14. Power factors as functions of output power for  $\gamma$ =1.78, max(f<sub>AC</sub>)=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{sw}=144$  kHz. The line inductance is  $L_1=44$  30 μH.

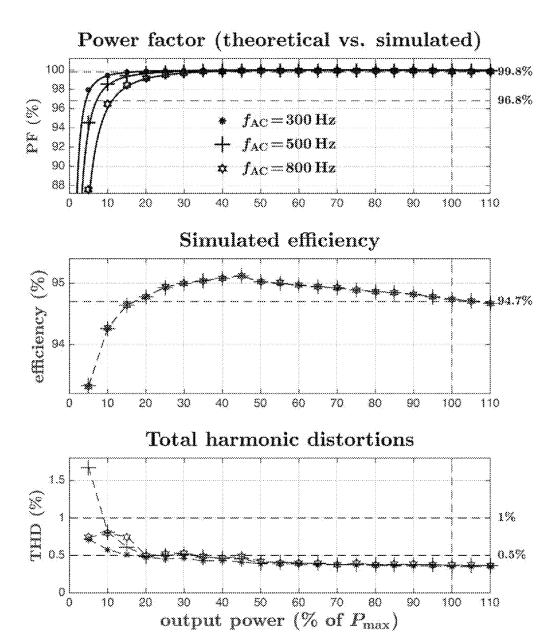

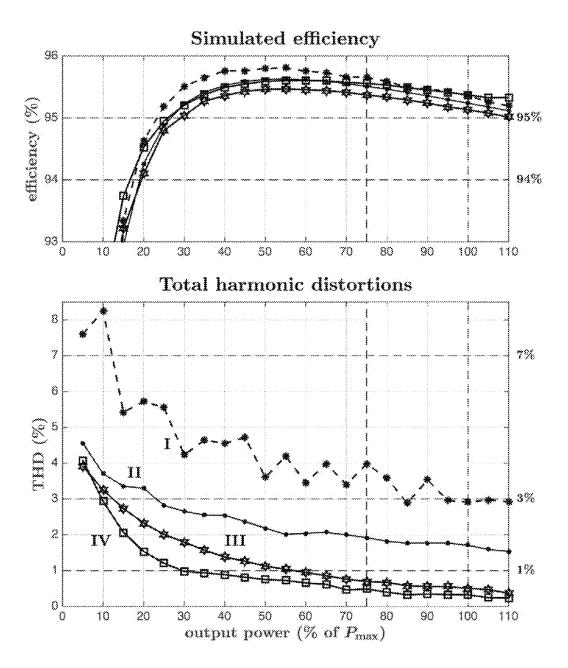

- FIG. 15. Simulated power factor, efficiency, and total harmonic distortions as functions of output power for  $f_{AC}$ =300 Hz,  $f_{AC}$ =500 Hz, and  $f_{AC}$ =800 Hz. ( $P_{max}$ =8.1 kW,  $f_{sw}$ =144 kHz, 115 VAC/270 VDC conversion.)

- FIG. 16. Example of line LC filtering network with parallel  $R_d$ - $L_d$  damping.

- FIG. 17. Current supplied to the output RC circuit as a sum of the output currents of the three sections.

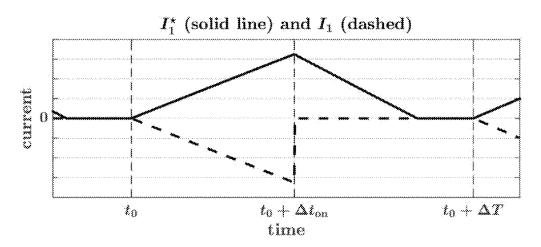

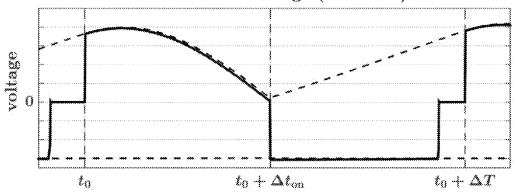

- FIG. 18. Voltage and current relations during switching 40 for the inductor in the 1st section.

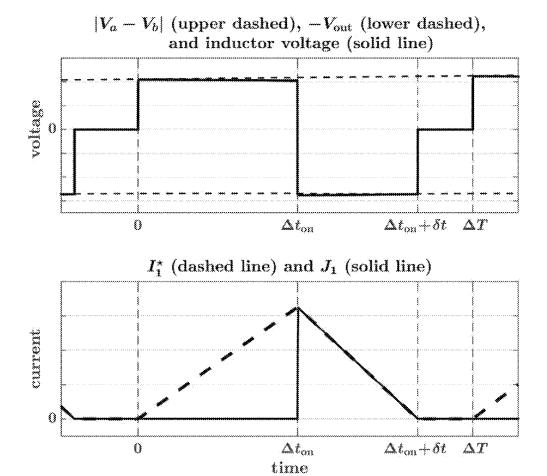

- FIG. 19. Duty cycle of a PWM with a "parabolic" wave

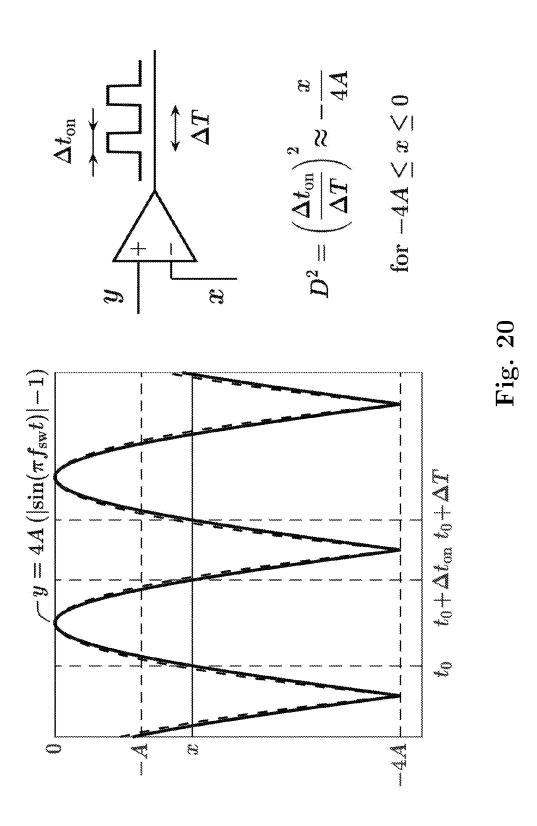

- FIG. 20. Duty cycle of a PWM with a full-wave rectified sine wave FCS.

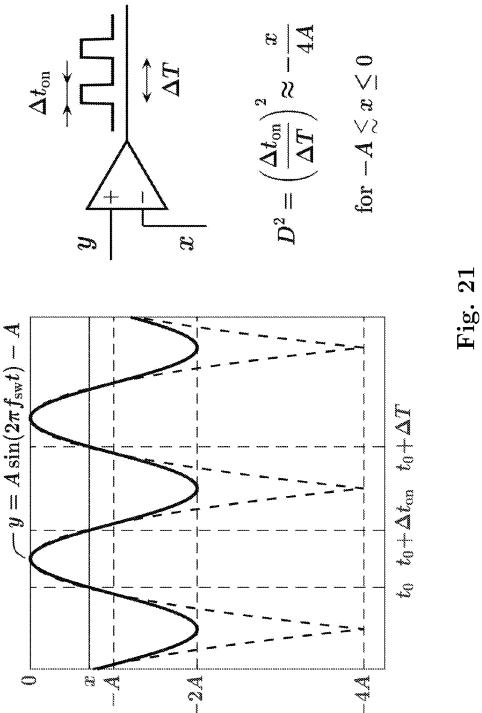

- FIG. 21. Duty cycle of a PWM with a sine wave FCS.

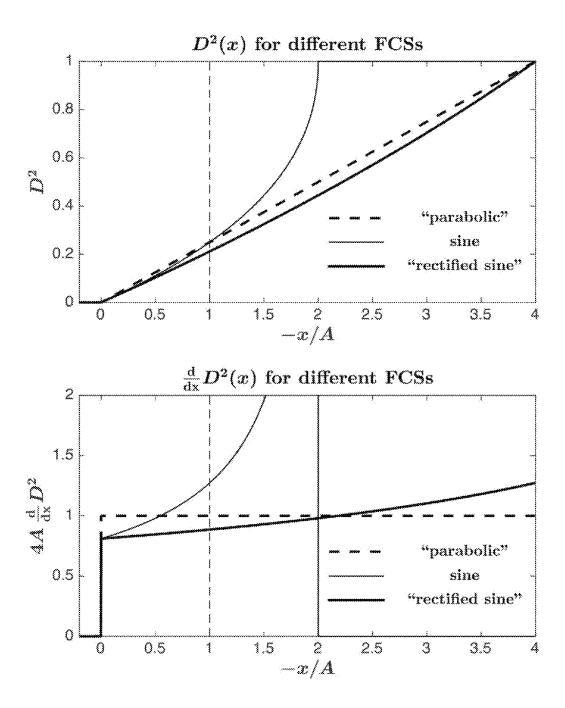

- FIG. 22.  $D^2$  and  $dD^2/dx$  as functions of x for the FCSs shown in FIGS. 19, 20, and 21.

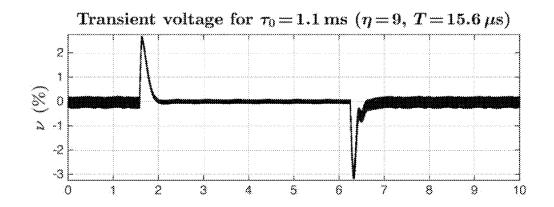

- FIG. 23. Reducing transients by increasing  $C_{ld}$ .

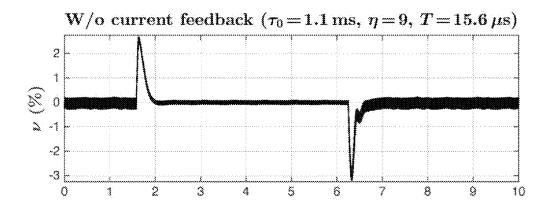

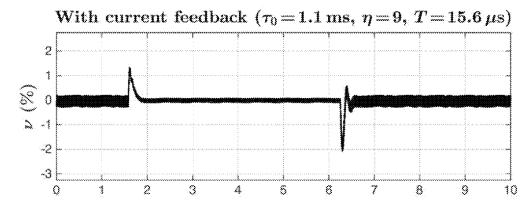

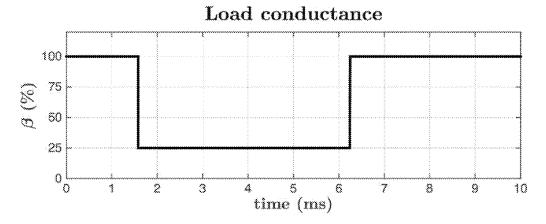

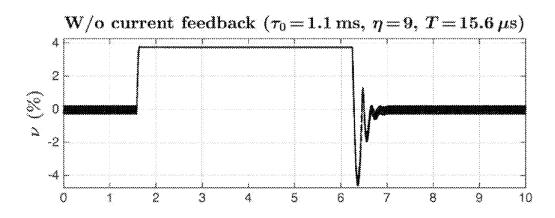

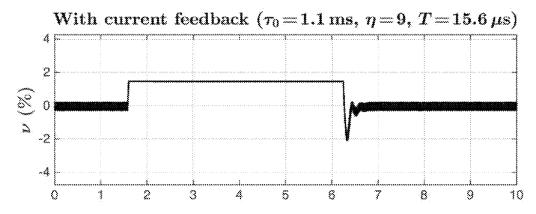

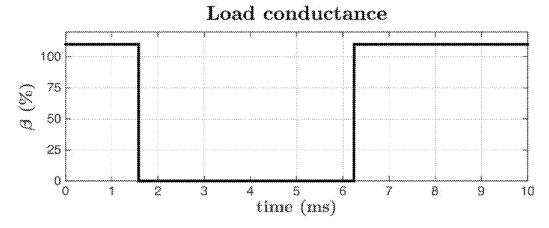

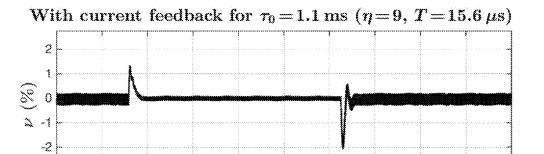

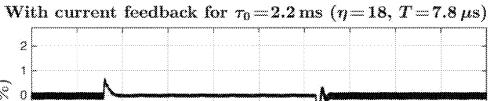

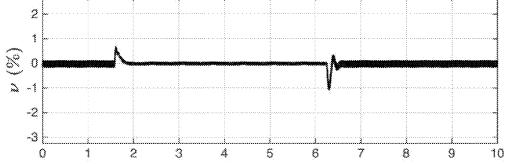

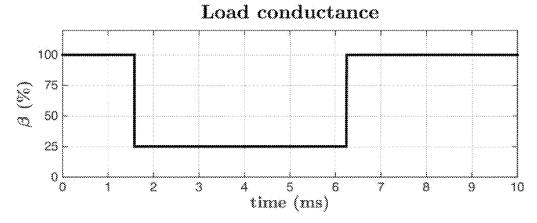

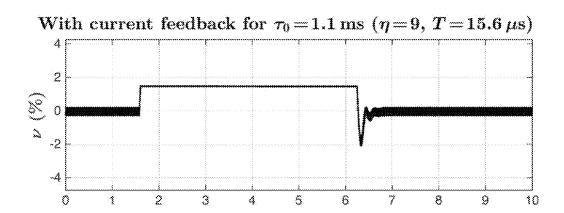

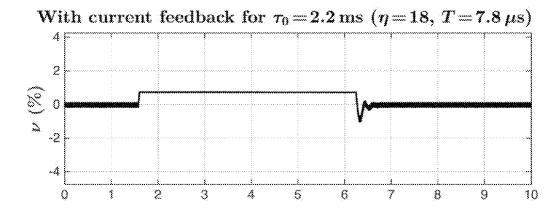

- FIG. 24. Reducing transients by using additional "cur- 50 rent" feedback.

- FIG. 25. Transients for load changes from open circuit to 10% overload (0-110% load change).

- FIG. 26. Further reducing transients by increasing  $C_{1d}$ (25-100% load change).

- FIG. 27. Further reducing transients by increasing  $C_{ld}$ (0-110% load change).

- FIG. 28. Reducing line current transients and output voltage "ringing" during large low-to-high load steps (0-110% load change). ( $P_{max}$ =8.1 kW,  $f_{sw}$ =144 kHz, 60  $f_{AC}$ =500 Hz, 115 VAC/270 VDC conversion.)

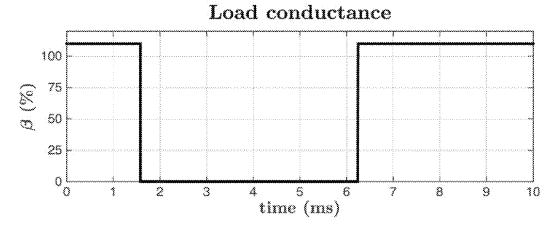

- FIG. 29. Example of converter output stage with EMI filtering network.

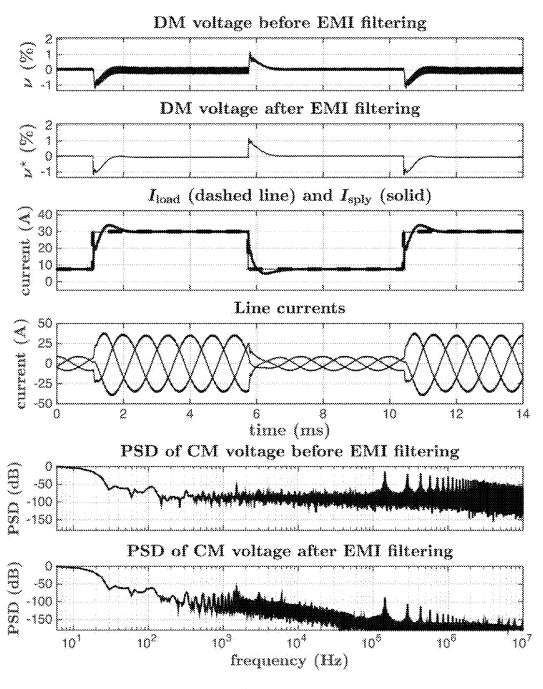

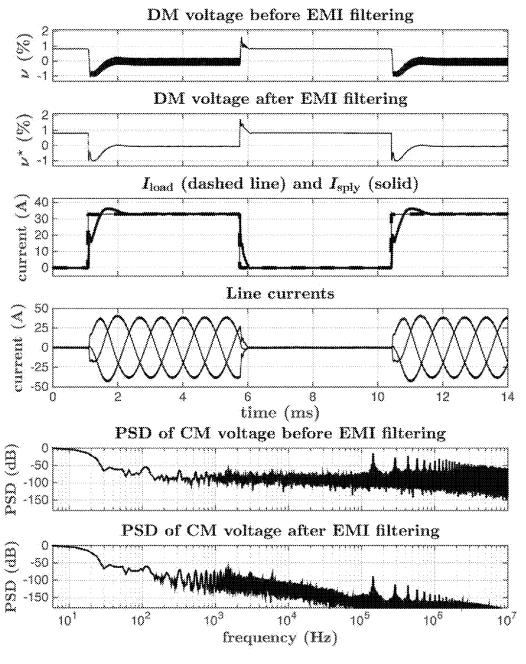

- FIG. 30. Example of currents and voltages in a converter with output EMI filtering (25-100% load steps). ( $P_{max}$ =8.1 kW,  $f_{sw}$ =144 kHz,  $f_{AC}$ =500 Hz, 115 VAC/270 VDC conver-

6

- FIG. 31. Example of currents and voltages in a converter with output EMI filtering (0-110% load steps). ( $P_{max}$ =8.1 kW,  $f_{sw}$ =144 kHz,  $f_{AC}$ =500 Hz, 115 VAC/270 VDC conver-

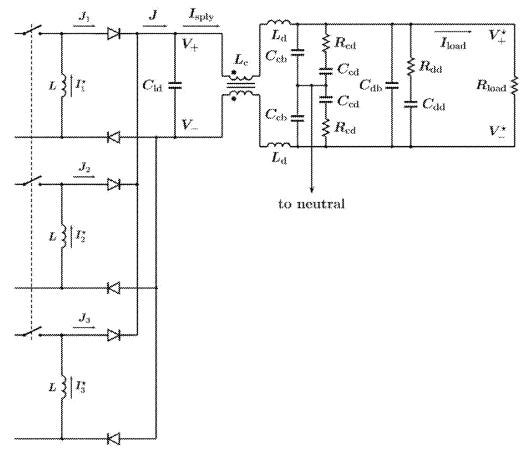

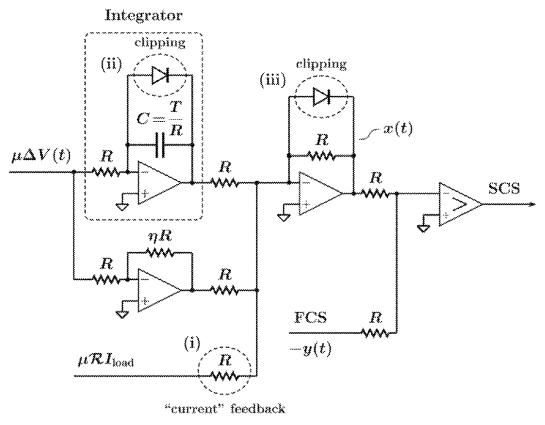

- FIG. 32. Example of controller circuit implementation.

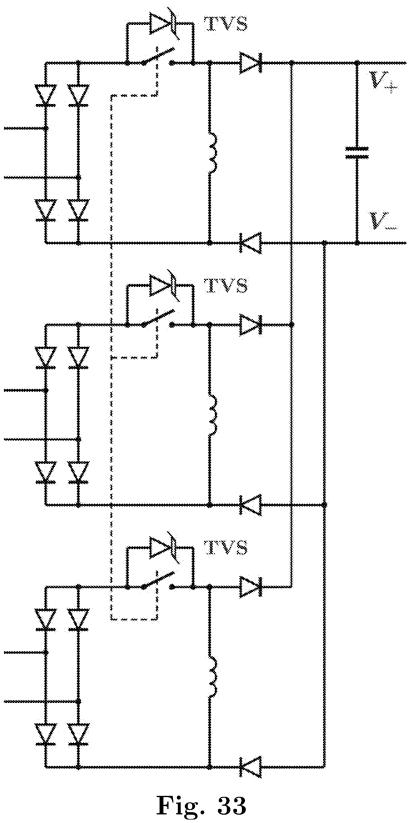

- FIG. 33. Limiting maximum voltages across switches by TVS diodes.

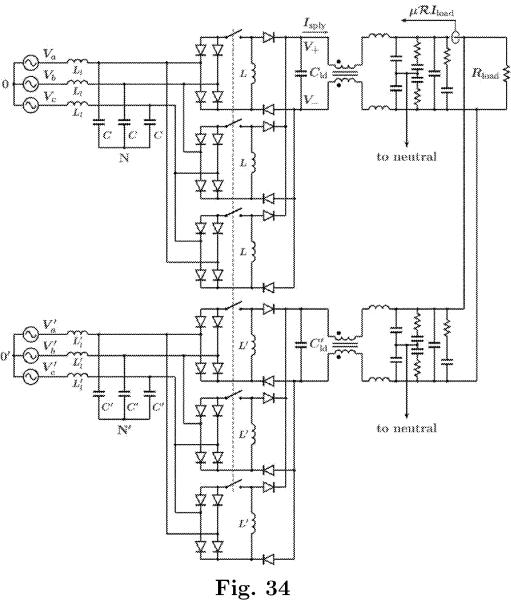

- FIG. 34. Example of parallel connection of two different ULSR converters.

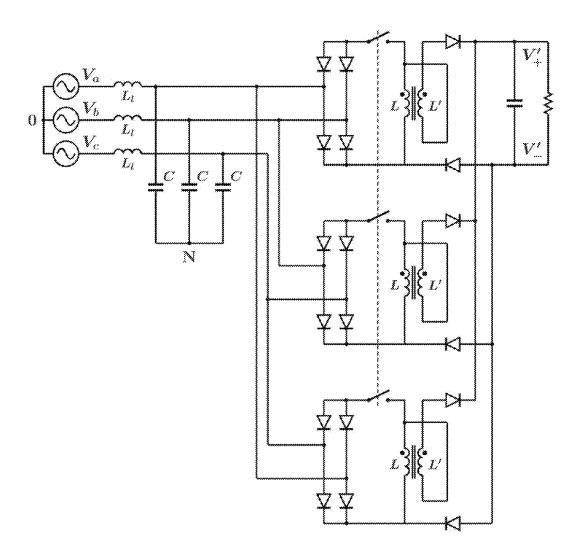

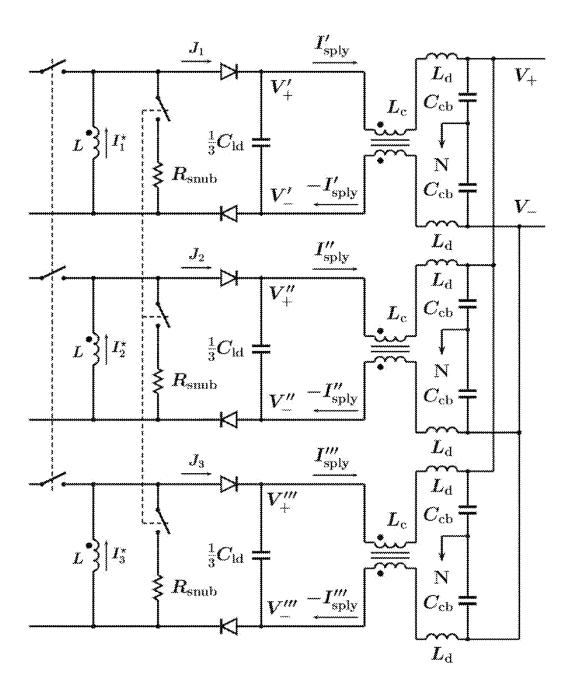

- FIG. 35. Idealized circuit diagram (without an output EMI filtering network) of an ULISR unit with step-up autotransformers replacing the converter inductors to increase the output voltage.

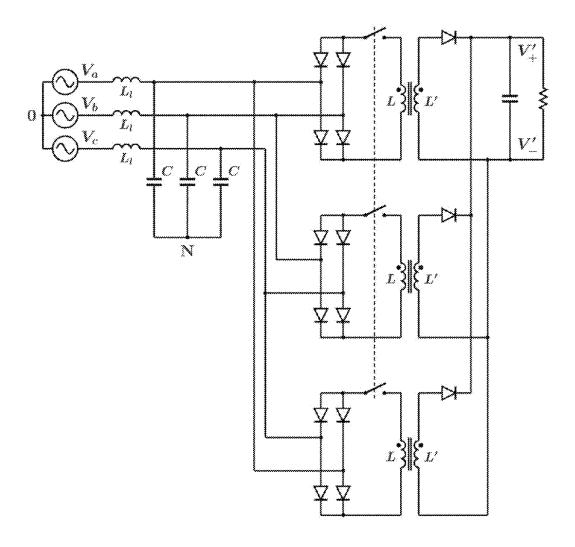

- FIG. 36. 3-phase boost AC-to-DC converter, with an LC frequency f<sub>sw</sub>=144 kHz. The line inductance is according to 15 filtering network inserted between the voltage sources and the power stage of the converter.

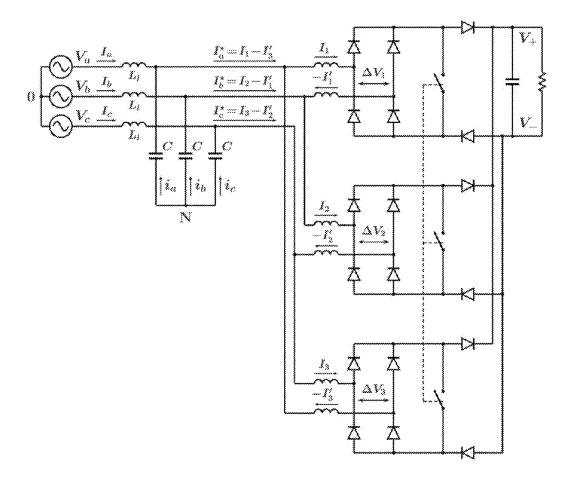

- FIG. 37. Idealized circuit diagram of an Ultra Linear Isolated Switching Rectifier (ULISR).

- FIG. 38. Illustration of effects of parasitic capacitances on on the line current.

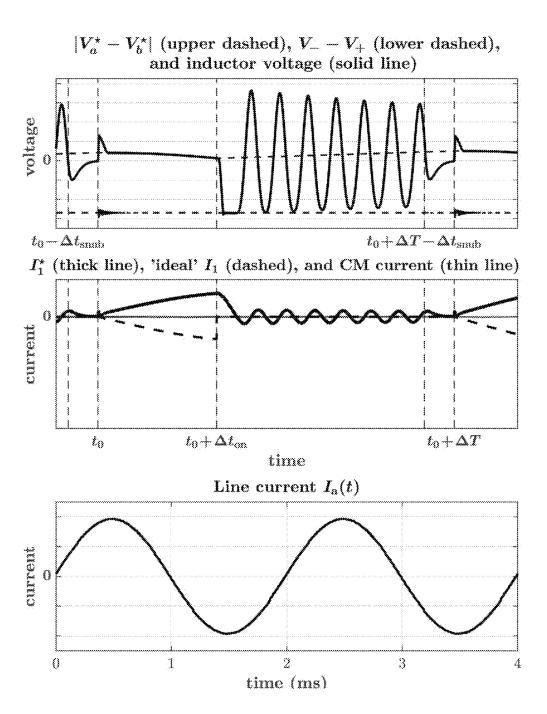

- FIG. 39. Example of an active snubber to ensure that the current in, and the voltage across, converter inductors in each ULSR section are effectively zero at the beginning and the end of any switching interval.

- FIG. 40. Illustration of reducing the effects of parasitic capacitances on the inductor voltage and current, and on the line current, by an active snubber shown in FIG. 39.

- FIG. 41. Example of CM section chokes added to reduce CM section currents.

- FIG. 42. Illustration of reducing the effects of parasitic capacitances on the inductor voltage and current, and on the line current, by an active snubber and CM section chokes, as shown in FIG. 41.

- FIG. 43. Illustrative comparison of efficiencies and THD of ULSR converters, as functions of output power, for ULSRs (i) without active snubber, section CM chokes, and converter inductors coupling (line type I), (ii) with active snubber only (line type II), (iii) with both active snubber and section CM chokes (line type III), and (iv) with the snubber, CM chokes, and converter inductor coupling (line type IV).  $(P_{max}=3 \text{ kW}, f_{sw}=144 \text{ kHz}, f_{AC}=500 \text{ Hz}, 115 \text{ VAC/270 VDC})$ conversion.)

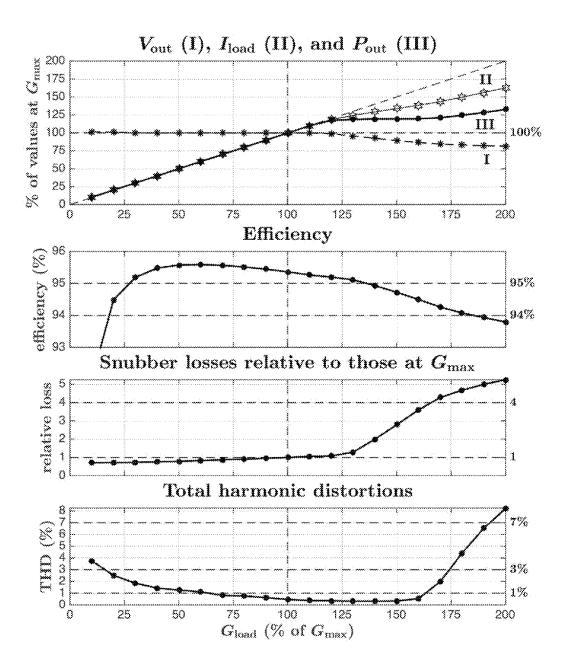

- FIG. 44. Example of the output voltages, currents, and powers (illustrating the current/power limiting), efficiency, THD, and losses in the snubber, as functions of the load conductance, for a ULSR with active snubber and section CM chokes. ( $P_{max}$ =3 kW,  $f_{sw}$ =144 kHz,  $f_{AC}$ =500 Hz, 115 VAC/270 VDC conversion.)

# **ABBREVIATIONS**

AC: alternating (current or voltage); ATRU: Auto-Transformer Rectifier Unit;

BOM: Bill Of Materials;

CCM: Continuous Conduction Mode; CM: Common Mode; COT: Constant On Time; COTS: Commercial Off-The-Shelf;

DC: direct (current or voltage), or constant polarity (current or voltage); DCM: Discontinuous Conduction Mode; DCR: DC Resistance of an inductor; DM: Differential Mode; DSP: Digital Signal Processing/Processor;

EMC: electromagnetic compatibility; EMF: electromotive force; EMI: electromagnetic interference; ESR: Equivalent Series Resistance:

FCS: Frequency Control Signal;

GaN: Gallium nitride;

IGBT: Insulated-Gate Bipolar Transistor;

LDO: low-dropout regulator; LED: Light-Emitting Diode:

MATLAB: MATrix LABoratory (numerical computing environment and fourth-generation programming language 5 developed by MathWorks); MEA: More Electric Aircraft; MOS: Metal-Oxide-Semiconductor; MOSFET: Metal Oxide Semiconductor Field-Effect Transistor; MTBF: Mean Time Between Failures:

NDL: Nonlinear Differential Limiter;

PF: Power Factor; PFC: Power Factor Correction; PoL: Point-of-Load; PSD: Power Spectral Density; PSM: Power Save Mode; PSRR: Power-Supply Rejection Ratio; PWM: Pulse-Width Modulator;

RFI: Radio Frequency Interference; RMS: Root Mean 15 Square;

SCS: Switch Control Signal; SiC: Silicon carbide; SMPS: Switched-Mode Power Supply; SMVF: Switched-Mode Voltage Follower; SMVM: Switched-Mode Voltage Mirror; SNR: Signal to Noise Ratio; SCC: Switch Control Circuit; 20

THD: Total Harmonic Distortion; TRU: Transformer Rectifier Unit:

UAV: Unmanned Aerial Vehicle; ULISR: Ultra Linear Isolated Switching Rectifier; ULSR(U): Ultra Linear Switching Rectifier (Unit);

VN: Virtual Neutral; VRM: Voltage Regulator Module; ZVS: Zero Voltage Switching;

#### DETAILED DESCRIPTION

As required, detailed embodiments of the present invention are disclosed herein. However, it is to be understood that the disclosed embodiments are merely exemplary of the invention that may be embodied in various and alternative forms. The figures are not necessarily to scale; some features 35 may be exaggerated or minimized to show details of particular components. Therefore, specific structural and functional details disclosed herein are not to be interpreted as limiting, but merely as a representative basis for the claims and/or as a representative basis for teaching one skilled in 40 the art to variously employ the present invention.

Moreover, except where otherwise expressly indicated, all numerical quantities in this description and in the claims are to be understood as modified by the word "about" in de-scribing the broader scope of this invention. Practice 45 within the numerical limits stated is generally preferred. Also, unless expressly stated to the contrary, the description of a group or class of materials as suitable or preferred for a given purpose in connection with the invention implies that mixtures or combinations of any two or more members 50 of the group or class may be equally suitable or preferred.

The detailed description of the invention is organized as follows

Section 1 ("Buck-boost 3-phase AC-to-DC converter") introduces the ULSR arrangement that may be viewed as a 55 three-phase diode bridge with an integrated buck-boost converter, and Subsection 1.1 ("Basic operation, voltage and current relations, and the inductor value for the converter shown in FIG. 1") describes its basic operation and the relations between its parameters and component values.

Section 2 ("Suppressing high-frequency component of line current") and its subsections 2.1 ("Virtual neutral capacitance for the converter shown in FIG. 6"), 2.2 ("Line inductance and power factor for the converter shown in FIG. 6"), 2.2.1 ("Preferred choice for line inductance for the 65 converter shown in FIG. 6 to meet power factor specifications"), and 2.3 ("Additional line EMI filtering and damp-

8

ing") discuss the constraints that may be imposed on the values of the virtual neutral capacitors and the line inductors in an LC filtering network inserted between the voltage sources and the converter in order to suppress high-frequency components of the line currents.

Section 3 ("Regulating the output of a buck-boost 3-phase AC-to-DC converter") and its subsections 3.1 ("Factors affecting transient response"), 3.2 ("Further improving transient response by introducing a feedback signal indicative of the load current"), 3.3 ("Light-load behavior and transitions to and from zero load"), 3.4 ("Further reducing line current transients and output voltage "ringing" during large low-to-high load steps"), 3.5 ("Output EMI filtering"), and 3.6 ("Example of controller circuit implementation") describe the method and corresponding apparatus for providing a robust and stable regulated converter output voltage for full range of output power (i.e. from full load to open circuit), characterized by small in magnitude and duration voltage and current transients in response to load changes.

Section 4 ("Additional discussion of ULSR converter, its modifications, and properties") and its subsections Subsection 4.1 ("Scaling to different range of output powers"), 4.2 ("Limiting maximum voltages across switches"), 4.3 ("Operation under heavily unbalanced mains voltages and/or in case of mains failure"), 4.4 ("Parallel connections to increase power and/or to provide N+1 redundancy"), 4.5 ("Stepping output voltage up or down with autotransformer"), and 4.6 ("Boost 3-phase AC-to-DC converter") provide additional discussion of ULSR converters, their modifications, and properties.

Section 5 ("Isolated buck-boost 3-phase AC-to-DC converter") introduces an isolated buck-boost 3-phase AC-to-DC converter, referred to as an Ultra Linear Isolated Switching Rectifier, or ULISR.

Section 6 ("Mitigating the effects of parasitic capacitances of semiconductor components and of bridge voltage drops") and Subsection 6.1 ("Further reduction of THD in ULSR by introducing coupling among converter inductors") discuss mitigating the effects of parasitic capacitances of semiconductor components and of bridge voltage drops.

Finally, Section 7 provides a few additional comments on the current disclosure.

## 1 Buck-Boost 3-Phase AC-to-DC Converter

Let us first consider an idealized circuit diagram of a 3-phase AC/DC converter shown in FIG. 1. This arrangement may be viewed as a three-phase diode bridge with an integrated buck-boost converter. One should be able to see that this converter may also be viewed as consisting of three identical sections connected in parallel to a common load. In this example, the load is represented by a parallel RC circuit. Each section comprises 6 diodes (4 of which are connected in a bridge), an inductor (with inductance L), and a switch.

It may be assumed here and further that the switches in all three sections operate synchronously, i.e., they are "on" (closed) and/or "off" (open) at the same time, as indicated by the dashed line drawn through the actuators of the switches. Thus these three switches may be viewed as one triple-pole, single-throw switch.

The main idealization of this diagram would be in assuming that the AC voltage sources are effectively ideal (e.g., effectively zero line inductance), and in neglecting non-idealities of the components, such as their parasitic capacitances. As a result, we would assume zero current in the reverse-bias direction of the diodes, and zero current through

One may see in FIG. 1 that a section of the converter comprises an inductor (a "converter inductor"), a diode bridge having two AC terminals and two DC terminals, a 1st output diode and a 2nd output diode, and an active switching device (a "switch"). The AC terminals of the bridge are also the input terminals of the section, and a 1st input voltage is applied to a 1st AC terminal, and a 2nd input voltage is applied to a 2nd AC terminal. The cathode of the 1st output diode is a positive output terminal of the section, and the anode of the 2nd output diode is a negative output terminal of the section.

One may further see in FIG. 1 that the anode of the 1st output diode is connected to a 1st terminal of the converter <sup>15</sup> inductor, forming a 1st node, and that the cathode of the 2nd output diode is connected to a 2nd terminal of the converter inductor, forming a 2nd node.

Further, in FIG. 1 a 1st terminal of the switch is connected to a negative DC terminal of the diode bridge, a 2nd terminal 20 of the switch is connected to the 1st node, and a positive DC terminal of the bridge is connected to the 2nd node. Also, an alternative switch connection may be used, wherein a 1st terminal of the switch is connected to a positive DC terminal of the diode bridge, a 2nd terminal of the switch is connected 25 to the 2nd node, and a negative DC terminal of the bridge is connected to the 1st node.

One skilled in the art will recognize that diodes in the converter shown in FIG. 1 may be replaced with active semiconductor switches. For example, a diode bridge may be replaced by a synchronous MOSFET-based rectifying arrangement.

# 1.1 Basic Operation, Voltage and Current Relations, and the Inductor Value for the Converter Shown in FIG. 1

One should be able to see that the converter depicted in FIG. 1 is powered by three voltage sources providing the voltages  $V_a$ ,  $V_b$ , and  $V_c$ , and connected in a "Y" configuration. Thus the voltages applied to the three sections of the converter would be equal to the differences  $V_a - V_b$  (1st section),  $V_b - V_c$  (2nd section), and  $V_c - V_a$  (3rd section), respectively.

Let us assume that the switches operate at a fixed switching frequency and with a given duty cycle, so that the duration of a full switching interval is  $\Delta T$ =const, and the duration of the interval during which the switches are in the "on" position (allowing the current to flow through the switch) is  $\Delta t_{on}$ =const $\Delta T$ . Let us further assume that the 50 converter operates in a discontinuous conduction mode (DCM), so that the inductor current in each section is zero at the beginning (and, therefore, at the end) of any switching interval.

Let us now examine the voltage and current relations 55 during a switching interval for the inductor in the 1st section, as illustrated in FIG. 2. One should be able to see from FIG. 1 that, ignoring the voltage drops across the diodes and the switch, during the "on" time the voltage across the inductor would be equal to the absolute value of the voltage applied 60 to the section, i.e., to  $|V_a-V_b|$ , causing the inductor current to increase. Also, the inductor current during the "on" time would be equal to the absolute value of the current supplied to the section,  $|I_1|$ . During the initial phase of the switch "off" time, the inductor current would forward bias the 65 "output" diodes, and the voltage across the inductor would be equal (ignoring the diodes' forward voltage drop) to the

10

output voltage difference  $V_-V_+$ , causing the inductor current to decrease. Since the converter operates in a DCM, at the final phase of the switch "off" time both the inductor current and the voltage across the inductor would be equal to zero. Also, the current I supplied to the section would be equal to zero during the entire switch "off" interval.

With the above, the average value  $<I_1>$  of the current  $I_1$  supplied to the 1st section during a full switching interval starting at  $t_0$  may be expressed as

$$\langle I_1 \rangle = \frac{1}{\Delta T} \int_{t_0}^{t_0 + \Delta t_{om}} dt I_1(t) = \frac{\Delta t_{om}^2}{2L\Delta T} \overline{V}_{ob} \propto \overline{V}_{ob}, \tag{1}$$

where  $\nabla_{ab}$  is the voltage  $V_a(t) - V_b(t)$  evaluated at some instance within the "on" position of the switch. For example, if the switch is turned on at time  $t_0$ , then  $\nabla_{ab} = V_a(t) - V_b(t)$ , where  $\bar{t}$  is such that  $t_0 \leq \bar{t}_0 + \Delta t_{an}$ .

One may see from equation (1) that for a sufficiently small  $\Delta t_{on}$  the average values over a full switching interval of the supply current and the supply voltage would be proportional to each other.

Let us now consider the converter shown in FIG. 1 wherein the voltage sources supply balanced 3-phase voltages with the AC frequency  $f_{AC} = T_0^{-1}$ . For the initial simplicity of the subsequent discussion, let us also assume that the switching frequency  $f_{sw} = \Delta T^{-1}$  is such that  $f_{sw} = 6N$   $f_{AC}$ , where N is an integer. Then, from the symmetries that should be apparent in FIG. 1, the following relations among the currents and voltages would hold (with practical accuracy limited by non-idealities):

$$V_b(t) = V_a(t - T_0/3),$$

$V(t)=V_a(t-2T_0/3),$

35

$$V_a(t)+V_b(t)+V_c(t)=0,$$

(2)

$I_b(t) = I_a(t - T_0/3),$

$I_c(t) = I_a(t - 2T_0/3),$

$$I_a(t)+I_b(t)+I_c(t)=0,$$

(3)

$I_2(t)=I_1(t-T_0/3),$

$I_3(t)=I_1(t-2T_0/3),$

$$I_1(t)+I_2(t)+I_3(t)=0,$$

(4)

and

$I_2*(t)=I_1*(t-T_0/3),$

$$I_3*(t)=I_1*(t-2T_0/3).$$

(5)

From equation (1) it would follow that

$$I_1(t) = G[V_a(t) - V_b(t)] + \Delta I_1(t),$$

(6)

where G is a constant (with physical units of conductance) and  $\Delta I_1(t)$  is a zero-mean current with the main frequency content consisting of the harmonics of the switching frequency±the AC frequency. Similarly,

$$I_3(t) = G[V_c(t) - V_a(t)] + \Delta I_3(t)$$

(7)

Since from equation (2) it follows that  $V_a - V_b - (V_c - V_a) = 3V_a$ , the line current  $I_a(t)$  may be expressed as

$$I_a(t)=I_1(t)-I_3(t)=3GV_a(t)+\Delta I_a(t),$$

(8)

11

where  $\Delta I_a(t)$  is a zero-mean current with the main frequency content consisting of the harmonics of the switching frequency±the AC frequency.

Likewise,

$$I_b(t) = I_2(t) - I_1(t) = 3GV_b(t) + \Delta I_b(t),$$

(9) 5

and

$$I_c(t)=I_3(t)-I_2(t)=3GV_c(t)+\Delta I_c(t)$$

. (10)

One should be able to see from equations (8), (9), and (10) that, ignoring the frequency content with frequencies at  $f_{sw}$ - $f_{AC}$  and above, the line currents in the converter shown in FIG. 1 would be proportional to the respective line voltages.

This is illustrated in FIG. 3 for the line voltage  $V_a(t)$  and the respective line current  $I_a(t)$  for the converter shown in FIG. 1 with the following values: The line frequency is  $f_{AC}$ =500 Hz, the switching frequency is  $f_{sw}$ =78 $f_{AC}$ =39 kHz, the conductance of the load is  $G_{load}$ = $R_{load}$ <sup>-1</sup>= $(9\Omega)$ <sup>-1</sup>, the output voltage is  $V_{out}$ = $V_+$ - $V_-$ =270 V (the output power is  $P_{out}$ =8.1 kW), the RMS of the line-to-neutral voltage is  $V_{LN}$ =115 V, and the inductance is L=39  $\mu$ H.

One skilled in the art will recognize that equations (3), (4), and (5) may not generally hold for the instantaneous current values if  $f_{sw} \neq 6N$   $f_{AC}$ . However, one will also recognize that these equations may still adequately represent the current relations for the current values averaged over a full switching interval, provided that the switching frequency is sufficiently high, e.g.,  $f_{sw} \ge 100$   $f_{AC}$ . Thus equations (8), (9), and (10) would still hold, and, ignoring the frequency content with frequencies at  $f_{sw} - f_{AC}$  and above, the line currents in the converter shown in FIG. 1 would still be proportional to the respective line voltages.

This is illustrated in FIG. 4 for the converter shown in FIG. 1 with the following values: The line frequency is  $f_{AC}$ =500 Hz, the switching frequency is  $f_{sw}$ =80 $f_{AC}$ =40 kHz, the conductance of the load is  $G_{load}$ = $R_{load}^{-1}$ =(9 $\Omega$ )<sup>-1</sup>, the output voltage is  $V_{out}$ = $V_{+}$ - $V_{-}$ =270 V (the output power is  $P_{out}$ =8.1 kW), the RMS of the line-to-neutral voltage is  $V_{LN}$ =115 V, and the inductance is L=39  $\mu$ H.

One skilled in the art will recognize that if the product of the resistance and the capacitance of the load is sufficiently large so that the voltage  $V_+$ – $V_-$  across the load may be considered constant, then the conductance G may be expressed as

$$G = \frac{1}{3} \frac{(V_+ - V_-)^2}{V_-^2 + V_c^2 + V_c^2} G_{lood} = \frac{1}{9} \frac{V_{out}^2}{V_{out}^2} G_{lood} = \frac{1}{9} \frac{P_{out}}{V_{Out}^2}, \tag{11}$$

where  $V_{out}=V_+-V_-$ ,  $G_{load}=R_{load}^{-1}$  is the conductance of the load,  $V_{LN}$  is the RMS of the line-to-neutral voltage, and  $P_{out}$  is the output power.

The voltage conversion ratio  $V_{out}/V_{LN}=3\sqrt{6}/\pi\approx 2.34$  may be of a particular interest, as it would correspond to the 55 conversion ratio of a three-phase full-wave diode rectifier. For this ratio,  $G^{-1}=\pi^2R_{load}/6\approx 5R_{load}/3$ .

The maximum duty cycle  $D'_{max}$  for which the converter shown in FIG. 1 would always operate in a DCM may be expressed as follows:

$$D'_{max} = \frac{\max(\Delta t_{on})}{\Delta T} = \frac{1}{1 + \frac{\max(V_a - V_b)}{V_{out}}} = \frac{1}{1 + \sqrt{6} \frac{V_{LN}}{V_{out}}}.$$

(12)

12

For example,  ${\rm D'}_{max}=1/(1+\pi/3)\approx 1/2$  (for  ${\rm V}_{out}/{\rm V}_{LN}=3\sqrt{6}/\pi$  (e.g., for  ${\rm V}_{LN}=115{\rm V}$  and  ${\rm V}_{out}=270{\rm V}$ ).

When operating at  $D'_{max}$ , the conductance G would have the maximum value  $G_{max}$ ,

$$G_{max} = \frac{1}{9} \frac{V_{out}^2}{V_{IN}^2} \max(G_{load}) = \frac{1}{9} \frac{P_{max}}{V_{IN}^2},$$

(13)

where  $P_{max}$  is the maximum output power of the converter. Thus the maximum value of the inductance  $L_{max} = max(L)$  for which the converter shown in FIG. 1 would always operate in a DCM may be expressed as follows:

$$L_{max} = \frac{9D'_{max}^2 V_{LN}^2 \Delta T}{2P_{max}} = \frac{3V_{out}^2}{4f_{sw} P_{max} \left(1 + \frac{V_{out}}{V_{LN} \sqrt{6}}\right)^2}.$$

(14)

For example, L<sub>max</sub>=44 µH for V<sub>LN</sub>=115 V, V<sub>out</sub>=270 V, P<sub>max</sub>, =8.1 kW, and  $\Delta$ T=25  $\rho$ s (f<sub>sw</sub>=40 kHz).

However, if the line voltage is reduced to  $V_{LN}$ =90 V,  $L_{max}$ =34  $\mu H$  to ensure a DCM operation for the same maximum output power.

FIG. **5** plots the maximum duty cycle D'<sub>max</sub> (upper panel) and the maximum value of the converter inductance  $L_{max}$  (lower panel) according to equations (12) and (14), respectively, as functions of the voltage conversion ratio  $V_{out}/V_{LN}$ .

In a design of a practical converter for given  $f_{sw}$ ,  $V_{out}$ , and  $P_{max}$ , and operable at a minimum line voltage min( $V_{LN}$ ), the inductance value for the converter inductor may be chosen

$$L = \frac{3V_{out}^2}{4f_{sw}P_{max}\left(1 + \frac{V_{out}}{\min(V_{LN})\sqrt{6}}\right)^2} \le L_{max}.$$

(15)

Then the "actual" maximum duty cycle  $D_{max}$  of the converter (while operating at maximum power and at minimum line voltage) may be expressed as

$$D_{max} = \frac{\sqrt{2Lf_{sw}P_{max}}}{3\min(V_{IN})} \le D'_{max}. \tag{16}$$

# 2 Suppressing High-Frequency Component of Line Current

To suppress the high-frequency component of the line current, let us insert an LC filtering network between the voltage sources and the converter, as shown in FIG. 6. For convenience, let us refer to an inductor L<sub>I</sub> as a "line inductor", to an inductor L as a "converter inductor", and to a capacitor C as a "virtual neutral capacitor", or "VN capacitor".

Depending on the converter specifications (e.g., voltage conversion and power rating, and the switching frequency) and the converter inductance, the values for the line inductors and the virtual neutral capacitors would need to be chosen in a proper way to ensure high power factor and efficiency, and low harmonic distortions of the line current.

The constraints that may be imposed on the values of the virtual neutral capacitors and the line inductors are discussed in this section.

# 2.1 Virtual Neutral Capacitance for the Converter Shown in FIG. 6

Let us first assume that the line inductance  $L_I$  is sufficiently large so that the line currents  $I_a$ ,  $I_b$ , and/or  $I_c$  may be considered constant during a switching interval. It may be then shown that a sufficient (albeit not necessary) condition for the current through a converter inductor to be an increasing function of time during an "on" position of the switch (i.e., during any  $\Delta t_{an}$  interval) may be expressed as

$$D_{max}\Delta T \le \frac{1}{4}2\pi\sqrt{L\frac{C}{2}} \,, \tag{17}$$

leading to

$$C \ge \frac{8}{\pi^2} \frac{D_{\text{max}}^2 \Delta T^2}{L}. \tag{18}$$

Then the minimum value of the VN capacitance  $C_{min}$  that ensures an increasing current through a converter inductor during any  $\Delta t_{on}$  interval may be expressed as

$$C_{min} = \frac{16}{9\pi^2} \frac{P_{max}}{f_{5w} \min(V_{LN})^2}.$$

(19)

For example,  $C_{min}\approx$  3.6  $\mu$ F for  $P_{max}=$  8.1 kW, min( $V_{LN}$ )=100 V, and  $\Delta$ T=25  $\rho$ s (40 kHz switching).

One should be able to see from equations (14) and (19) that, for given voltage and current specifications, both  $L_{max}$  and  $C_{min}$  are inversely proportional to the switching frequency  $f_{sw} = \Delta T^{-1}$ .

FIG. 7 provides an example of voltage and current relations during switching for the inductor in the 1st section of the converter shown in FIG. 6 with  $C = C_{min}$  ( $V_{LN} = \min$  ( $V_{LN}$ )). One may see in this figure that at the end of a  $\Delta t_{on}$  45 interval the inductor voltage approaches zero, and the rate of increase in the inductor current becomes small (close to zero).

FIG. **8** provides an example of voltage and current relations during switching for the inductor in the 1st section of 50 the converter shown in FIG. **6** with  $C \approx \frac{3}{4} C_{min}$  ( $V_{LN}$ =min ( $V_{LN}$ )). One may see in this figure that the inductor voltage approaches zero, and that the rate of change in the inductor current becomes effectively zero before the end of a  $\Delta t_{on}$  interval. Thus an increase (and/or a small decrease) in the 55 duty cycle would not result in a change in the output current, and thus the output may no longer be regulated.

FIG. 9 provides an example of voltage and current relations during switching for the inductor in the 1st section of the converter shown in FIG. 6 with  $C \approx 2C_{min}$  ( $V_{LN}$ =min 60 ( $V_{LN}$ )). One may see in this figure that the variation in the voltage  $|V_a^* - V_b^*|$  is reduced, and that the current in the converter inductor remains approximately linear during a  $\Delta t_{on}$  interval.

One should be able to see from the examples of FIGS. 7 65 through 9 that the value of the VN capacitance  $C \approx 2C_{min}$  provides approximately linearly increasing current in the

14

converter inductor during a  $\Delta t_{on}$  interval. Also, while with  $C \le C_{min}$  the switch is turned "off" at zero or small voltage (e.g., ZVS switch off-time), and thus switching losses may be reduced, such smaller VN capacitance values may result in relatively larger average currents in the bridge diodes and the switches, and thus in lower overall converter efficiency.

# 2.2 Line Inductance and Power Factor for the Converter Shown in FIG. 6

Clearly, inserting an LC filtering network between the voltage sources and the converter would affect the converter power factor (PF), which for a given converter would now be a function of both the line frequency f<sub>AC</sub> and the output power P<sub>out</sub> (or conductance of the load G<sub>load</sub>). Thus both the value of the VN capacitance C and the value of the line inductance L<sub>I</sub> need to be properly chosen to ensure a high power factor in full range of the line frequencies and in a desired range of the output powers, while remaining as small as possible for smaller weight, size, and cost.

While the VN capacitance C may be chosen in a relatively simple way as  $C_{min} < C \le 2C_{min}$ , this section provides a discussion and some guidelines for choosing the value of the line inductance  $L_I$  based on certain design requirements for the power factor. One skilled in the art will recognize that there may be a variety of alternative approaches to choosing this value.

In reference to FIG. 6, various current and voltage relations may be expressed as

$$I_{\sigma}(t) = I_{\sigma}^{*}(t) - i_{\sigma}(t) = \frac{1}{L_{l}} \int dt [V_{\sigma}(t) - V_{\sigma}^{*}(t)],$$

(20)

$$i_a(t) = -C\dot{V}_a^*(t),$$

(21)

$$V_a^*(t) = \overline{V}_a^*(t) + \Delta V_a^*(t), \tag{22}$$

and

$$I_a(t) = \overline{I}_a(t) + \Delta I_a(t), \tag{23}$$

where the overbar may be viewed to denote a centered moving average with interval  $\Delta T$ , and  $\Delta$  (as in  $\Delta V_a^*(t)$  and/or  $\Delta I_a(t)$ )—a residual high-frequency component.

Further, from the previous discussion, the current  $I_a^*(t)$  may be expressed as

$$I_a^*(t) = 3G^*\overline{V}_a^*(t) + \Delta I_a^*(t),$$

(24)

where  $G^*$  is a constant with physical units of conductance, and  $\Delta I_a^*(t)$  is a zero-mean current with the main frequency content consisting of the harmonics of the switching frequency±the AC frequency.

Since the switching frequency is much larger than the line frequency (e.g.,  $f_{sw} \ge 100 \, f_{AC}$ ), one skilled in the art will recognize that from equations (20) through (24) it would follow that

$$\overline{V}_{a}^{*}(t) = V_{a}(t) - 3L_{l}G^{*}\overline{V}_{a}^{*}(t) - L_{l}C\overline{V}_{a}^{*}(t)$$

$$\tag{25}$$

and

$$\overline{I}_{a}(t) = 3G^*\overline{V}_{a}^*(t) + C\overline{\dot{V}}_{a}^*(t). \tag{26}$$

One skilled in the art will further recognize that, according to equation (25),  $\nabla_a^*(t)$  may be viewed as the line

voltage  $V_{\it a}(t)$  filtered with a 2nd order lowpass filter with the undamped natural frequency  $\omega_0$  and the quality factor Q that may be expressed as

$$\omega_0 = \frac{1}{\sqrt{L_l C}} \text{ and } Q = \frac{1}{3G^*} \sqrt{\frac{C}{L_l}}, \qquad (27)$$

respectively. If  $V_a(t)=V_0\sin(2\pi f_{AC}\,t)$ , then, for a sufficiently large  $\omega_0$  (e.g., for  $\omega_0^2>>4\pi^2f_{AC}^2$ ),  $\nabla_a^*(t)$  may be expressed as  $\nabla_a^*(t)=V_0\sin(2\pi f_{AC}\,t-\phi)$ , where

$$\tan(\phi) \approx 6\pi L_1 G^* f_{AC} \tag{28}$$

Assuming that  $G^*$  is of the same order of magnitude as G (which would be typically true), and using equation (11),  $^{15}$  equation (28) may be rewritten as

$$\tan(\varphi) \approx \frac{2\pi}{3} L_I \frac{P_{out}}{V_{IN}^2} f_{AC}.$$

(29)

For example, for  $P_{out}$ =8.1 kW,  $V_{LN}$ =115 V, and  $f_{AC}$ =1 kHz,  $\tan(\phi)$ =1.28×10<sup>3</sup> Hz  $\Omega^{-1}$  L<sub>1</sub>.

Further, from equation (26)

$$\begin{split} \bar{I}_{a}(t) &= 3G^{*}V_{0}\bigg[\sin(2\pi f_{AC}t - \varphi) + \frac{2\pi}{3}f_{AC}\frac{C}{G^{*}}\cos(2\pi f_{AC}t - \varphi)\bigg] \\ &= 3G^{*}V_{0}\cos(\varphi)[\mathbf{b}\sin(2\pi f_{AC}t) + \alpha'\cos(2\pi f_{AC}t)], \end{split} \tag{30}$$

where

$$\alpha' = \frac{2\pi}{3} f_{AC} \frac{C}{G^*} - \tan(\varphi) = 2\pi f_{AC} \left( \frac{C}{3G^*} - 3G^* L_l \right), \tag{31}$$

and

$$b=1+(2\pi f_{AC})^2 L_I C.$$

(32)

Then the power factor may be expressed as

$$PF = \frac{\langle \bar{l}_a V_a \rangle}{\langle \bar{l}_a^2 \rangle^{\frac{1}{2}} \langle V_a^2 \rangle^{\frac{1}{2}}} = \frac{1}{\sqrt{1 + \left(\frac{\alpha'}{\mathbf{b}}\right)^2}} = \frac{1}{\sqrt{1 + \alpha^2}},$$

(33)

where the angular brackets denote time averaging over a large time interval, and where

$$\alpha = \frac{2\pi f_{AC}}{1 + (2\pi f_{AC})^2 L_4 C} \left(\frac{C}{3G^*} - 3G^* L_4\right). \tag{34}$$

One may further note that  $\alpha \approx \alpha'$  for  $\omega_0^2 >> 4\pi^2 f_{AC}^2$ .

Let us now choose the converter inductance as  $L=L_{max}$  according to equation (14), and the VN capacitance as 60  $C=\gamma C_{min}$ ,

$$C = \gamma C_{min} = \gamma \frac{16}{9\pi^2} \frac{P_{max}}{f_{sw} V_{LN}^2},$$

(35)

where  $\gamma$ >1 is a parameter that would be typically not much larger than unity (e.g.,  $\gamma$ =2).

Let us further choose the line inductance as  $L_I = \kappa L_0$ , where

$$L_0 = \frac{1}{4\pi^2 \operatorname{Cmax}(f_{r,c})^2},$$

(36)

and where  $\kappa << 1$ .

Assuming that the conductance G\* may be expressed as

$$G^* = \frac{1}{9} \frac{P_{out}}{V_{\ell N}^2},$$

(37)

and that the output power  $P_{out}$  is expressed as a fraction of the maximum power  $P_{max}$  (i.e.,  $P_{out} = \beta P_{max}$ , where  $0 < \beta \le 1$ ), substitution of equations (35) through (37) into equation (34) would lead to the following expression for  $\alpha$  as a function of the output power:

$$\alpha = \alpha(\beta; \gamma, f_{AC}, \kappa) = \frac{32\gamma f_{AC}}{3\pi\beta f_{sw}} \left[ 1 - \kappa \left( \frac{3\pi\beta f_{sw}}{32\gamma_{max}(f_{AC})} \right)^2 \right]$$

$$\approx \frac{3.4\gamma f_{AC}}{\beta f_{sw}} \left[ 1 - \kappa \left( \frac{\beta f_{sw}}{3.4\gamma_{max}(f_{AC})} \right)^2 \right],$$

(38)

where  $0 \le \beta \le 1$ ,  $\gamma > 1$ , and  $\kappa < < 1$ .

A possible choice for the parameter  $\kappa$  would be to ensure a unity power factor at some specified load  $P_{out}=\beta_0 P_{max}$ . With this,

$$\kappa = \left(\frac{32\gamma \max(f_{AC})}{3\pi\beta_0 f_{ww}}\right)^2 \approx \left(\frac{3.4\gamma \max(f_{AC})}{\beta_0 f_{ww}}\right)^2, \tag{39}$$

and equation (38) would become

(33)

$$\alpha = \alpha(\beta; \gamma, f_{AC}, \beta_0) \approx \frac{3.4\gamma f_{AC}}{\beta f_{sw}} \left[ 1 - \left( \frac{\beta}{\beta_0} \right)^2 \right]. \tag{40}$$

With  $\kappa$  given by equation (39), the line inductance  $L_{\text{I}}$  may be expressed as

$$L_l = \gamma \left(\frac{4}{\pi \beta_0}\right)^2 \frac{V_{LN}^2}{P_{max} f_{sw}}.$$

(41)

For example, L=110  $\mu$ H for P<sub>max</sub>=8.1 kW, V<sub>LN</sub>=115 V, f<sub>sw</sub>=48 kHz,  $\gamma$ =2, and  $\beta$ <sub>0</sub>=1 (i.e., PF=1 at maximum load). Another attractive choice for  $\kappa$  would be

$$\kappa = \frac{\max(f_{AC})}{f_{sw}},\tag{42}$$

65 and thus the resonant frequency of the L<sub>1</sub>C circuit is the geometric mean of the switching frequency and the maximum line frequency,

$$\frac{1}{2\pi\sqrt{L_iC}} = \sqrt{f_{sw} \max(f_{AC})}.$$

(43)

With  $f_{sw}>=\max(f_{AC})$ , this choice would ensure that both conditions  $\kappa<<1$  and  $\omega_0>>4\pi^2$   $f_{AC}^{\phantom{AC}}$  are met.

If the VN capacitance is given by equation (35),  $\kappa$  according to equation (42) would lead to the value for the line inductance as

$$L_{l} = \frac{9}{64\gamma} \frac{V_{LN}^{2}}{P_{max} \max(f_{AC})},\tag{44}$$

which is independent of the switching frequency. For example, L<sub>7</sub>=144  $\mu H$  for  $P_{max}$ =8.1 kW,  $V_{LN}$ =115 V,  $\gamma$ =2, and max(f $_{AC}$ )=800 Hz.

We then may write the following expression for  $\alpha$  as a  $_{20}$  function of the output power:

$$\alpha = \alpha(\beta; \gamma, f_{AC}) \approx \frac{3.4 \gamma f_{AC}}{\beta f_{sw}} \left[ 1 - \left( \frac{\beta}{3.4 \gamma} \right)^2 \frac{f_{sw}}{\max(f_{AC})} \right]. \tag{45}$$

Let us examine the values of  $\alpha$ , and the respective power factor values, for different output powers.

For full output power ( $\beta$ =1),

$$|\alpha(1; \gamma, f_{AC})| = \frac{3.4\gamma f_{AC}}{f_{sw}} \left| \left( \frac{1}{3.4\gamma} \right)^2 \frac{f_{sw}}{\max(f_{AC})} - 1 \right|$$

$$< \frac{f_{AC}}{3.4\gamma \max(f_{AC})} < \frac{1}{3.4\gamma},$$

(46)

provided that the switching frequency is sufficiently high, i.e.,  $f_{sw} \ge (3.4\gamma)^2 \max(f_{AC})$ . Then

$$\begin{split} PF(1;\,\gamma,\,f_{AC}) &\approx 1 - \frac{1}{2} |\alpha(1;\,f_{AC})|^2 \\ &> 1 - \left(\frac{f_{AC}}{4.8\gamma \text{max}(f_{AC})}\right)^2 > 1 - \frac{1}{(4.8\gamma)^2}. \end{split} \tag{47}$$

For example, for  $\gamma$ =2 the minimum power factor at full output power would be >98.9% in full range of line frequencies.

One should note that the minimum power factor given by equation (47) would be achieved in the limit of high switching frequencies, e.g., for  $f_{sw}>>(3.4\gamma)^2\max(f_{AC})$ , and that the full-load power factor would be generally higher for lower switching frequencies, e.g., for  $f_{sw}\geq(3.4\gamma)^2\max(f_{AC})$ . For 55 example, for  $\gamma=2$  and  $\max(f_{AC})=800$  Hz,  $(3.4\gamma)^2\max(f_{AC})=37$  kHz, and for the switching frequency  $f_{sw}=48$  kHz the full-load power factor at  $f_{AC}=800$  Hz would be  $\approx 99.94\%$ .

The power factor would become unity at  $\beta = \beta_0$  given by

$$\beta_0 \approx 3.4 \gamma \sqrt{\frac{\max(f_{AC})}{f_{sw}}} \ . \tag{48}$$

For example, for  $\gamma$ =2 and max( $f_{AC}$ )=800 Hz,  $\beta_0$ =0.878 (87.8%) for  $f_{sw}$ =48 kHz, and  $\beta_0$ =0.507 (50.7%) for  $f_{sw}$ =144

kHz. One would note that, if the line inductance is chosen according to equation (44), the switching frequency would need to be larger than  $(3.4\gamma)^2 \max(f_{AC})$  (e.g.,  ${\ge}37$  kHz for  $\gamma{=}2$  and  $\max(f_{AC}){=}800$  Hz) in order to achieve a unity power factor at some load.

For  $\beta < \beta_0$ , the power factor would be an increasing function of output power, becoming zero in the limit  $\beta \rightarrow 0$ . For sufficiently small  $\beta$  (e.g., resulting in a small power factor such that PF<sup>2</sup><<1),

$$PF(\beta; \gamma, f_{AC}) \approx \frac{f_{sw}}{3.4\gamma f_{AC}} \beta$$

for sufficiently small  $\beta$ . (49)

For  $\beta = \beta_{min}$  such that

$$\beta_{min} \approx \frac{3.4\gamma}{\sqrt{2\Delta PF_{max}}} \frac{\max(f_{AC})}{f_{sw}},$$

(50)

$$|\alpha(\beta_{min}; \gamma, \max(f_{AC}))| = \sqrt{2\Delta P F_{max}} \left| 1 - \frac{1}{2\Delta P F_{max}} \frac{\max(f_{AC})}{f_{sw}} \right|$$

(51)

provided that  $\Delta PF_{max} \ge \max(f_{AC})/(2f_{sw})$ . Then, for  $\max(f_{AC})/(2f_{sw}) \le \Delta PF_{max} <<1$ , the power factor would remain relatively large, namely

$$PF(\beta_{min} \le \beta \le \beta_0; \gamma, \max(f_{AC})) \ge 1 - \Delta PF_{max}.$$

(52)

For example, for  $\gamma$ =2, max(f<sub>AC</sub>)=800 Hz, f<sub>sw</sub>=144 kHz, and  $\Delta$ PF<sub>max</sub>=0.03 (3%), the power factor would remain above 97% for output powers larger than 15.4% of P<sub>max</sub>.

One should note that the power factor  $1-\Delta PF_{max}$  would be achieved for  $\beta_{min}$  given by equation (50) in the limit of high switching frequencies, e.g., for  $f_{sw} > \max(f_{AC})/(2\Delta PF_{max})$ , and that the power factor at  $\beta_{min}$  would be generally higher than  $1-\Delta PF$  for lower switching frequencies.

than  $1-\Delta PF_{max}$  for lower switching frequencies. For  $\Delta PF_{max} = 0.03$  (3%) and the line inductance according to equation (44), FIG. 10 shows the power factors as functions of output power for  $\gamma = 2$ ,  $\max(f_{AC}) = 800$  Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{sw} = 48$  kHz.

For  $\Delta PF_{max}$ =0.03 (3%) and the line inductance according to equation (44), FIG. 11 shows the power factors as functions of output power for  $\gamma$ =2, max( $f_{AC}$ )=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{sw}$ =144 kHz.

For  $\Delta PF_{max}$ =0.03 (3%) and the line inductance according to equation (44), FIG. 12 shows the power factors as functions of output power for  $\gamma$ =2, max( $f_{AC}$ )=800 Hz, line frequencies 300 Hz (thin line), 550 Hz (dashed line), 800 Hz (thick line), and switching frequency  $f_{exc}$ =480 kHz.

# 2.2.1 Preferred Choice for Line Inductance for the Converter Shown in FIG. 6 to Meet Power Factor Specifications

Let us now revisit the expression for a given by equation (40). At full power  $\beta$ =1, and the power factor

$$\alpha = \alpha(1; \gamma, f_{AC}, \beta_0) \approx \frac{3.4 \gamma f_{AC}}{f_{sw}} \left(1 - \frac{1}{\beta_0^2}\right),$$

(53)

(54)

$$PF(1; \gamma, f_{AC}, \beta_0) = 1 - \Delta PF_{max}$$

$$\begin{split} &\approx 1 - \frac{1}{2} |\alpha(1; \gamma, f_{AC}, \beta_0)|^2 \\ &\approx 1 - \frac{1}{2} \bigg( \frac{3.4 \gamma f_{AC}}{f_{sw}} \bigg)^2 \bigg( 1 - \frac{1}{\beta_0^2} \bigg)^2. \end{split}$$

Then a unity power factor would be achieved at 10  $P_{out} = \beta_0 P_{max}$ , where

$$\beta_0 \approx \frac{1}{\sqrt{1 + \frac{f_{sw}}{3.4\gamma f_{AC}} \sqrt{2\Delta P F_{max}}}}.$$

(55)

For example,  $\beta_0\approx2/3$  for  $\Delta PF_{max}=10^{-3}$  (99.9% power factor),  $f_{sw}=144$  kHz,  $f_{AC}=800$  Hz, and  $\gamma=1.9$ .

The line inductance may then be given by equation (41). For example,  $L_1 \approx 78.5 \mu H$  for  $P_{max} = 8.1 \text{ kW}$ ,  $V_{LN} = 115 \text{ V}$ ,  $f_{sw} = 144 \text{ kHz}, \gamma = 1.9, \text{ and } \beta_0 = 2/3.$

For  $\beta < \beta_0$ , the power factor would be an increasing function of output power, becoming zero in the limit  $\beta \rightarrow 0$ . 25 For  $\beta = \beta_{min}$  such that the power factor is  $1 - \Delta PF_{max}$ , we may

$$PF(\beta_{min}; \gamma, f_{AC}, \beta_0) = 1 - \Delta PF_{max}$$

$$\approx 1 - \frac{1}{2} |\alpha(\beta_{min}; \gamma, f_{AC}, \beta_0)|^2$$

$$\approx 1 - \frac{1}{2} \left(\frac{3.4\gamma f_{AC}}{f_{sw}}\right)^2 \left(\frac{1}{\beta_{min}} - \frac{\beta_{min}}{\beta_0^2}\right)^2,$$

(56)

and thus

$$\beta_{min} = \beta_0 \left( -K + \sqrt{K^2 + 1} \right), \tag{57}$$

where

$$K = \frac{\beta_0 f_{3W}}{4.8 \gamma f_{AC}} \sqrt{\Delta P F_{max}}.$$

(58)

For example, with  $f_{sw}=144$  kHz,  $f_{AC}=800$  Hz,  $\gamma=1.9$ , and  $\beta_0 = 2/3$ ,  $\beta_{min} \approx 0.445$  (44.5%) for  $\Delta PF_{max} = 10^{-3}$  (99.9% power factor), and  $\beta_{min} \approx 0.136$  (13.6%) for  $\Delta PF_{max} = 0.032$  (96.8%) power factor).

For the line inductance according to equation (41) (e.g., 55  $P_{out} = \beta_0 P_{max}$ , where L<sub>1</sub>≈78.5 μH for  $P_{max}$ =8.1 kW,  $V_{LN}$ =115 V,  $f_{sw}$ =144 kHz, γ=1.9, and  $β_0$ =2/3), FIG. **13** plots the power factors as functions of output power for  $max(f_{AC})=800$  Hz and the line frequencies 300 Hz (thin line), 550 Hz (dashed line), and 800 Hz (thick line).

Let us now consider a particular design example for a converter desired to convert a  ${\rm V}_{\!\mathit{LN}}\!\!=\!\!115$  VAC voltage with maximum frequency  $max(f_{AC})=800$  Hz into a  $V_{out}=270$ VDC voltage, and to operate at up to 8.1 kW of output

Let us first choose the switching frequency as  $f_{sw}=144$ kHz.

From equation (14),  $L_{max}=12.2 \mu H$ , and, using  $\approx 10\%$ tolerance margin, we may choose the converter inductance as

$$L=11 \mu H.$$

(59)

From equation (19),  $C_{min}$ =0.766 µF, and we may choose

e.g., two 0.68 µF capacitors connected in parallel, which would lead to

$$\gamma \approx 1.78$$

. (61)

Let us initially require that  $\Delta PF_{max}=10^{-3}$ . For this, the power factor is larger than 99.9%, and may be considered effectively unity. For  $\Delta PF_{max}=10^{-3}$ ,  $\beta_0$  given by equation (55) would be  $\beta_0$ =0.655, and the line inductance according 15 to equation (41) would be  $L_i=76 \mu H$ .

Let us further assume that due to design constraints  $L_1$ =44  $\mu$ H. This would lead to the following value for  $\beta$ <sub>0</sub>:

$$\beta_0 = \frac{3V_{LN}^2}{P_{max}} \sqrt{\frac{C}{L_l}} \approx 0.86 > 0.655.$$

(62)

For this  $\beta_0$ , the power factor at full load would be

$$PF(1; \gamma, f_{AC}, \beta_0) \approx 1 - \frac{1}{2} \left( \frac{3.4 \gamma f_{AC}}{f_{sw}} \right)^2 \left( 1 - \frac{1}{\beta_0^2} \right)^2 \ge 0.9999 (99.99\%)$$

(63)

for any line frequency  $f_{AC} \le \max(f_{AC})$ , and may be considered effectively unity.

The value  $\beta_{min}$  for which the power factor still remains above 99.9% would be

$$\beta_{min} \approx 0.499,\tag{64}$$

or less than half of the maximum power, and the power factor would remain above 96.8% for the loads>13%.

For this particular example, FIG. 14 plots the power factors as functions of output power for the line frequencies 300 Hz (thin line), 550 Hz (dashed line), and 800 Hz (thick

Let us consider another design example, for a converter with  $f_{sw}$ =144 kHz transforming a  $V_{LN}$ =115 VAC voltage with maximum frequency max( $f_{AC}$ )=800 Hz into a  $V_{out}$ =270 VDC voltage, and operating at up to  $P_{max}$ =8.1 kW of output power.

From equation (14),  $L_{max}$ =12.2  $\mu$ H, and the choice L=10

$\mu$ H would provide us with  $\approx$ 20% tolerance margin. From equation (19),  $C_{min}$ =0.766  $\mu$ F, and the VN capacitance value of C=1.2 µF (y≈1.57) would ensure (in combination with the reduced converter inductance, and thus smaller maximum duty cycle) that the current through a converter inductor would be an increasing function of time during an "on" position of the switch.

For  $L_i=60 \mu H$ , a unity power factor would be achieved at

$$\beta_0 = \frac{3V_{LN}^2}{P_{max}} \sqrt{\frac{C}{L_l}} \approx 0.69.$$

(65)

The power factor would be given by equation (33), where a would be given by equation (40).

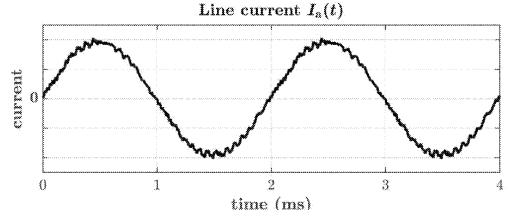

FIG. 15 provides examples of power factor, efficiency, and total harmonic distortions as functions of output power for  $f_{AC}$ =300 Hz,  $f_{AC}$ =500 Hz, and  $f_{AC}$ =800 Hz, simulated using LTspice IV for such a converter constructed with Commercial Off-The-Shelf (COTS) components. ( $P_{max}$ =8.1 kW,  $f_{sw}$ =144 kHz, 115 VAC/270 VDC conversion.) In these examples, the theoretical power factors are shown by the solid lines, and the output voltage regulation is performed by a controller constructed according to the disclosure provided in Section 3.

It would need to be noted, however, that the THD values shown in the examples of FIG. 15 assume employing additional means to mitigate the effects of parasitic capacitances of the semiconductor components (i.e., the diodes and the MOSFET power switches), as discussed in more detail in Section 6 of this disclosure.

## 2.3 Additional Line EMI Filtering and Damping

To meet various requirements on the conducted input EMI emissions, an additional filter for suppressing the input common and differential mode EMI may need to be inserted between the voltage sources and the LC filtering network. Also, such an EMI filter may need to incorporate additional 20 damping.

Indeed, for example, if the line inductance is chosen according to equation (41), then equation (27) may be rewritten as

$$f_0 = \frac{\omega_0}{2\pi} = \frac{3\pi\beta_0}{32\gamma} f_{sw} \text{ and } Q = \beta_0 \frac{P_{max}}{P_{out}},$$

(66)

and, with the constraints on  $\gamma$  and  $\beta_0$  as discussed above,

$$0.07 f_{sw} \lesssim f_0 \lesssim 0.3 f_{sw}$$

and  $\frac{1}{2} \frac{P_{max}}{P_{out}} \lesssim Q \leq \frac{P_{max}}{P_{out}}$ . (67)

Thus for light loads the quality factor may be significantly large, and damping may need to be employed.

In practice, it may be sufficient to incorporate such additional damping in the EMI filtering network. When 40 adding damping directly to the LC filtering network is required, parallel  $R_{a}$ - $L_{d}$  damping may be used, as illustrated in FIG. 16.

When additional line EMI filtering and/or damping is employed, the value of the line inductor  $\rm L_{\it l}$  may need to be 45 adjusted to meet the desired criteria for the power factor.

# 3 Regulating the Output of a Buck-Boost 3-Phase AC-to-DC Converter

It may be shown that the output voltage of the converter disclosed in Sections 1 and 2 would not only depend on the input voltage and the duty cycle, but also on the converter inductor value, the switching frequency, and the output current. In this section, we describe the method and corresponding apparatus for providing robust and stable regulated converter output voltage for full range of output powers (i.e. from full load to open circuit).

Let us first assume a load that may be represented by a parallel RC circuit, and consider the current supplied to the 60 output RC circuit by the converter shown in FIG. 1 as a sum of the output currents of the three sections, as illustrated in FIG. 17.

Let us assume that  $\min(R_{load})C_{ld}\gg\Delta T$ , and thus we may neglect the high-frequency "ripples" in the output voltage. 65 For example, for  $C_{ld}=105~\mu F$ ,  $\min(R_{load})=9\Omega$ , and  $f_{sw}=144~kH$ ,  $\min(R_{load})C_{ld}f_{sw}=136>>1$ .

It may be then shown (see, for example, the illustration of the inductor voltage and current relations during switching depicted in FIG. 18) that the average value  $\langle J_1 \rangle$  of the current  $J_1$  supplied by the 1st section to the output RC circuit during a full switching interval may be expressed as

$$\langle J_1 \rangle = \frac{1}{\Delta T} \int_{\Delta loo}^{\Delta t_{on} + \delta t} dt I_1^*(t) = \frac{D^2 \overline{V}_{ob}^2}{2L f_{sy} V_{out}},$$

(68)

where D= $\Delta t_{op}/\Delta T$  is the duty cycle.

The average value <J> of the total current J supplied by all three sections to the output RC circuit during a full switching interval may then be expressed as

$$\langle J \rangle = \langle J_1 \rangle + \langle J_2 \rangle + \langle J_3 \rangle = D^2 \frac{\overline{V}_{ab}^2 + \overline{V}_{bc}^2 + \overline{V}_{ca}^2}{2L f_{sw} V_{out}} = D^2 \frac{9 V_{LN}^2}{2L f_{sw} V_{out}}. \tag{69}$$

<J> may also be expressed as the sum of the average currents through the capacitor and through the resistive load, namely as

$$\langle J \rangle = G_{load} \langle V_{out} \rangle + C_{ld} \langle \dot{V}_{out} \rangle.$$

(70)

If we may express  $V_{out}$  as  $V_{out} = V_{ref} + \Delta V$ , where  $V_{ref} = const$  and  $|\Delta V| << V_{ref}$ , then equating the right-hand sides of equations (69) and (70) and differentiating the resulting equality with respect to time would lead to the following expression:

$$\frac{d}{dt}D^2 - D^2 \dot{v} = \rho \dot{G}_{load} + \rho G_{load} \dot{v} + \rho G_{td} \dot{v}, \qquad (71)$$

where  $v=<\Delta V>/V_{ref}$  is nondimensionalized transient voltage, and

$$\rho = \frac{2Lf_{sw}V_{ref}^2}{9V_{LN}^2} \tag{72}$$

is a parameter (constant for  $V_{LN}$ =const) with physical units of resistance.

For example,  $\rho$ =1.94 $\Omega$  for L=11  $\mu$ H,  $f_{sw}$ =144 kHz,  $V_{ref}$ =270 V, and  $V_{LN}$ =115 V. Further, if  $C_{ld}$ =105  $\mu$ F, then  $\rho C_{ld}$ =204  $\rho$ s.

Let us now assume that the switches in the converter may be controlled by a two-level switch control signal (SCS) in such a way that a high level of the SCS corresponds to the "on" position of the switches, and a low level of the SCS corresponds to the "off" position.

Let us further assume that the SCS may be provided by a pulse-width modulator (PWM) comprising a comparator that compares a signal x(t) with a frequency control signal (FCS) y(t) and outputs a high-level SCS when y>x, and a low-level SCS when y<x.

If the FCS y(t) is such that, for a constant x,  $D^2$  is proportional to x ( $D^2 \propto x$ ) for  $0 < D \le D_{max}$ , then  $dD^2/dx$  would be a constant ( $dD^2/dx = const$ ) for  $0 < D \le D_{max}$ . If x(t) may be considered approximately constant (in relation to y(t)) during a  $\Delta T$  interval, and if, further, x(t) is a linear combination of y(t) and of an antiderivative of y(t) with respect to time

(fdt v(t)), then equation (71) for the nondimensionalized transient voltage v(t) may be approximated by a 2nd order linear differential equation.

An example of such an FCS that provides  $D^2 \propto x$  for 0 < D < 1 would be a "parabolic" wave as illustrated in FIG. 5 19. Such a parabolic FCS may be generated, e.g., by integrating a zero-mean sawtooth wave and applying appropriate scaling and translation. Also, a good approximation for such a parabolic FCS may be a full-wave rectified sine wave with frequency  $f_{sw}/2$ , appropriately scaled and translated, as illustrated in FIG. 20.

When the proportionality  $D^2 \propto x$  may be desired only for  $0 < D \le 1/2$  (e.g., when  $D_{max} \le 1/2$ ), a simple sine wave with frequency  $f_{sw}$  may also be used, as illustrated in FIG. 21. In the numerical examples (simulations) of this section, such a sine-wave FCS signal is used.

FIG. 22 illustrates  $D^2$  and  $dD^2/dx$  as functions of x for the FCSs shown in FIGS. 19, 20, and 21. Note that for all shown FCSs  $D^2$ =0 and

$$\frac{d}{dt}D^2 = 0 \text{ for } x > 0.$$

In the subsequent discussion of this section, it would also be assumed that

$$D^2 = -\frac{x}{4A},$$

and thus

$$\frac{d}{dx}D^2 = -\frac{1}{4A} = const, \text{ for } -4AD_{max}^2 \lesssim x < 0.$$

Thus the time derivative of  $D^2$  for  $-4A D_{max}^2 \le x < 0$  may be 40 expressed as

$$\frac{d}{dt}D^2 = -\frac{\dot{x}}{4A}. ag{73}$$

Let us further consider a signal x(t) that may be expressed as a linear combination of the transient voltage and of its antiderivative with respect to time,

$$x(t) = \mu \left[ \eta \Delta V(t) + \frac{1}{T} \int dt \Delta V(t) \right]. \tag{74}$$

The signal x(t) given by equation (74) may be interpreted as a sum of a feedback error signal  $\mu\Delta V(t)$  integrated by an integrator with the time constant T, and of a feedback error signal multiplied by the gain  $\eta$ .

The time derivative of x(t) may be expressed as

$$\dot{x}(t) = \frac{\mu V_{ref}}{T} [v(t) + \eta T \dot{v}(t)]. \tag{75} \label{eq:75}$$

Then for  $-4A D_{max} \le x < 0$  equation (71) for the nondimensionalized transient voltage v(t) may be rewritten as

$$v = -\lambda T \dot{\beta} - \left[ \eta + \left( \beta + \frac{R_{min}}{\rho} D^2 \right) \lambda \right] T \dot{v} - \lambda T \tau_0 \ddot{v}, \tag{76}$$

where  $R_{min} = min(R_{load})$ ,

$$\rho = \frac{2Lf_{sw}V_{ref}^2}{9V_{LN}^2} = D_{max}^2 R_{min} \left(\frac{\min(V_{LN})}{V_{LN}}\right)^2, \tag{77}$$

$$0 \le \beta = G_{load} R_{min} \le 1, \tag{78}$$

$$\tau_0 = R_{min} C_{ld} = \text{const},$$

(79)

$$\lambda = \lambda_0 \left( \frac{\min(V_{LN})}{V_{LN}} \right)^2 \le \lambda_0, \quad (80)$$

and where

20

25

$$\lambda_0 = \frac{4A_{\rho}}{\mu V_{ref} R_{min}} = \frac{8I f_{sw} A V_{ref}}{9 \mu R_{min} \min(V_{PN}^2)} = const.$$

(81)

<sup>30</sup> For example,  $λ_0$ =0.61 for A=1.6V, L=10 μH,  $f_{sw}$ =144 kHz, μ=10<sup>-2</sup>,  $R_{min}$ =9Ω,  $V_{ref}$ =270 V, and min( $V_{LN}$ )=100 V. Equation (76) may be further rewritten as

$$v = -\lambda T \dot{\beta} - \frac{\sqrt{\lambda T_{\tau_0}}}{Q} \dot{v} - \lambda T_{\tau_0} \ddot{v}, \tag{82}$$

where the quality factor Q may be expressed as

$$Q = \frac{\sqrt{\frac{\lambda_{\tau_0}}{T}}}{\eta + \left(\beta + \frac{R_{min}}{\rho}D^2\right)\lambda} \le Q_{max} = \frac{1}{\eta}\sqrt{\frac{\lambda_0\tau_0}{T}}.$$

(83)

A reasonable practical choice for the quality factor may be

$$\frac{1}{2} \lesssim Q_{max} \lesssim 1$$

.

55

This choice would provide fast transient response that is not significantly overdamped and/or underdamped.

# 3.1 Factors Affecting Transient Response

One may obtain from equation (82) that, for a step current (i.e., when  $\dot{\beta}(t)$  is proportional to the Dirac  $\delta$ -function [2]), 60 the duration  $\Delta t_{tr}$  of the transient may be expressed as

$$\Delta t_{tr} = \frac{\int_{0}^{\infty} dt t \nu(t)}{\int_{0}^{\infty} dt \nu(t)} = \frac{\sqrt{\lambda T \tau_0}}{Q},$$

(84)

and that, for a constant Q, both the magnitude and the duration of the output voltage transient would be proportional to

$\sqrt{T}$ .

On the other hand, from equation (83),

$$T = \frac{\lambda_0 \tau_0}{\eta^2 Q_{max}^2},\tag{85}$$

and both the magnitude and the duration of the step-current output voltage transient would be inversely proportional to the gain  $\eta$ . Thus one should choose as high gain  $\eta$  as practically reasonable without violating the validity of the approximations employed in derivation of equation (82), under various operational conditions.

In particular, since in derivation of the equations of this section we have been considering quantities averaged over a full switching interval  $\Delta T = f_{sw}^{-1}$ , one skilled in the art will recognize that, for a reasonably small  $Q_{max}$  (e.g.,  $Q_{max} \le 1$ ) a constraint on the gain i) may be expressed as

$$\eta \lesssim \frac{1}{\gamma} \lambda_0 f_{sw} \tau_0, \tag{86}$$

where  $\gamma$  is a constant of order 10 (e.g.,  $\gamma$ =10). For example,  $\eta$ <10 for  $\lambda_0$ =0.61,  $f_{sw}$ =144 kHz,  $\tau_0$ =1.1 ms, and  $\gamma$ =10.

Using equations (85) and (86), equation (82) may be rewritten as

$$v = -\frac{\xi^2}{f_{yw}^2 Q_{max}^2} \frac{\beta}{\tau_0} - \frac{\xi}{f_{sw} Q_{max}} \vec{v} \cdot -\frac{\xi^2}{f_{sw}^2 Q_{max}^2} \vec{v}, \tag{87}$$

where

$$\xi = \gamma \sqrt{\frac{\lambda}{\lambda_0}} \le \gamma. \tag{88}$$

One may notice that in equation (87) for the nondimensionalized transient voltage the parameter  $\xi$  does not depend 50 on particular voltage and current specifications, and/or particular choice of component values, as well as A and  $\mu$ .

One may also notice that Q and  $Q_{max}$  would be of the same order of magnitude for a sufficiently large  $\eta$  (e.g., for  $\eta >> 2\lambda_0$ ). One skilled in the art will thus recognize that, 55 according to equation (87), a decrease in  $Q_{max}$  would increase the duration of a transient,  $\Delta t_{tr} \propto Q_{max}^{-2}$ . The magnitude of the transient would also be a monotonically decreasing function of  $Q_{max}$ , approaching a maximum value in the limit  $Q_{max} \rightarrow 0$ .

A reasonable practical choice for the quality factor may be  $\frac{1}{2} \le Q_{max} \le 1$ . This choice would provide a fast transient response that is not significantly overdamped and/or underdamped, and would also ensure that the undamped natural frequency of the 2nd order lowpass filter represented by equation (87) would remain sufficiently smaller than the switching frequency.